Mojo 🔥 GPU Puzzles, Edition 1

“For the things we have to learn before we can do them, we learn by doing them.” Aristotle (Nicomachean Ethics)

Welcome to our hands-on guide to GPU programming using Mojo 🔥, the programming language that combines Python syntax with systems-level performance.

Start with this overview video, or continue reading below.

Why GPU programming?

GPU programming has evolved from a specialized skill into fundamental infrastructure for modern computing. From large language models processing billions of parameters to computer vision systems analyzing real-time video streams, GPU acceleration drives the computational breakthroughs we see today. Scientific advances in climate modeling, drug discovery, and quantum simulation depend on the massive parallel processing capabilities that GPUs uniquely provide. Financial institutions rely on GPU computing for real-time risk analysis and algorithmic trading, while autonomous vehicles process sensor data through GPU-accelerated neural networks for critical decision-making.

The economic implications are substantial. Organizations that effectively leverage GPU computing achieve significant competitive advantages: accelerated development cycles, reduced computational costs, and the capacity to address previously intractable computational challenges. In an era where computational capability directly correlates with business value, GPU programming skills represent a strategic differentiator for engineers, researchers, and organizations.

Why Mojo🔥 for GPU programming?

The computing industry has reached a critical point. CPU performance no longer increases through higher clock speeds due to power and heat constraints. Hardware manufacturers have shifted toward increasing physical cores. This multi-core approach reaches its peak in modern GPUs, which contain thousands of cores operating in parallel. The NVIDIA H100, for example, can run 16,896 threads simultaneously in a single clock cycle, with over 270,000 threads queued for execution.

Mojo provides a practical approach to GPU programming, making this parallelism more accessible:

- Python-like Syntax with systems programming capabilities

- Zero-cost Abstractions that compile to efficient machine code

- Strong Type System that catches errors at compile time

- Built-in Tensor Support with hardware-aware optimizations for GPU computation

- Direct Access to low-level CPU and GPU intrinsics

- Cross-Hardware Portability for code that runs on both CPUs and GPUs

- Improved Safety over traditional C/C++ GPU programming

- Lower Barrier to Entry for more programmers to access GPU power

Mojo🔥 aims to fuel innovation by democratizing GPU programming. >By expanding on Python’s familiar syntax while adding direct GPU access, Mojo allows programmers with minimal specialized knowledge to build high-performance, heterogeneous (CPU, GPU-enabled) applications.

Why learn through puzzles?

Most GPU programming resources start with extensive theory before practical implementation. This can overwhelm newcomers with abstract concepts that only become clear through direct application.

This book uses a different approach: immediate engagement with practical problems that progressively introduce concepts through guided discovery.

Advantages of puzzle-based learning:

- Direct experience: Immediate execution on GPU hardware provides concrete feedback

- Incremental complexity: Each challenge builds on previously established concepts

- Applied focus: Problems mirror real-world computational scenarios

- Diagnostic skills: Systematic debugging practice develops troubleshooting capabilities

- Knowledge retention: Active problem-solving reinforces understanding more effectively than passive consumption

The methodology emphasizes discovery over memorization. Concepts emerge naturally through experimentation, creating deeper understanding and practical competency.

Acknowledgement: The Part I and III of this book are heavily inspired by GPU Puzzles, an interactive NVIDIA GPU learning project. This adaptation reimplements these concepts using Mojo’s abstractions and performance capabilities, while expanding on advanced topics with Mojo-specific optimizations.

The GPU programming mindset

Effective GPU programming requires a fundamental shift in how we think about computation. Here are some key mental models that will guide your journey:

From sequential to parallel: Eliminating loops with threads

In traditional CPU programming, we process data sequentially through loops:

# CPU approach

for i in range(data_size):

result[i] = process(data[i])

GPU programming inverts this paradigm completely. Rather than iterating sequentially through data, we assign thousands of parallel threads to process data elements simultaneously:

# GPU approach (conceptual)

thread_id = get_global_id()

if thread_id < data_size:

result[thread_id] = process(data[thread_id])

Each thread handles a single data element, replacing explicit iteration with massive parallelism. This fundamental reframing—from sequential processing to concurrent execution across all data elements—represents the core conceptual shift in GPU programming.

Fitting a mesh of compute over data

Consider your data as a structured grid, with GPU threads forming a corresponding computational grid that maps onto it. Effective GPU programming involves designing this thread organization to optimally cover your data space:

- Threads: Individual processing units, each responsible for specific data elements

- Blocks: Coordinated thread groups with shared memory access and synchronization capabilities

- Grid: The complete thread hierarchy spanning the entire computational problem

Successful GPU programming requires balancing this thread organization to maximize parallel efficiency while managing memory access patterns and synchronization requirements.

Data movement vs. computation

In GPU programming, data movement is often more expensive than computation:

- Moving data between CPU and GPU is slow

- Moving data between global and shared memory is faster

- Operating on data already in registers or shared memory is extremely fast

This inverts another common assumption in programming: computation is no longer the bottleneck—data movement is.

Through the puzzles in this book, you’ll develop an intuitive understanding of these principles, transforming how you approach computational problems.

What you will learn

This book takes you on a journey from first principles to advanced GPU programming techniques. Rather than treating the GPU as a mysterious black box, the content builds understanding layer by layer—starting with how individual threads operate and culminating in sophisticated parallel algorithms. Learning both low-level memory management and high-level tensor abstractions provides the versatility to tackle any GPU programming challenge.

Your current learning path

| Essential Skill | Status | Puzzles |

|---|---|---|

| Thread/Block basics | ✅ Available | Part I (1-8) |

| Debugging GPU Programs | ✅ Available | Part II (9-10) |

| Core algorithms | ✅ Available | Part III (11-16) |

| MAX Graph integration | ✅ Available | Part IV (17-19) |

| PyTorch integration | ✅ Available | Part V (20-22) |

| Functional patterns & benchmarking | ✅ Available | Part VI (23) |

| Warp programming | ✅ Available | Part VII (24-26) |

| Block-level programming | ✅ Available | Part VIII (27) |

| Advanced memory operations | ✅ Available | Part IX (28-29) |

| Performance analysis | ✅ Available | Part X (30-32) |

| Modern GPU features | ✅ Available | Part XI (33-34) |

Detailed learning objectives

Part I: GPU fundamentals (Puzzles 1-8) ✅

- Learn thread indexing and block organization

- Understand memory access patterns and guards

- Work with both raw pointers and TileTensor abstractions

- Learn shared memory basics for inter-thread communication

Part II: Debugging GPU programs (Puzzles 9-10) ✅

- Learn GPU debugger and debugging techniques

- Learn to use sanitizers for catching memory errors and race conditions

- Develop systematic approaches to identifying and fixing GPU bugs

- Build confidence for tackling complex GPU programming challenges

Note: Debugging puzzles require

pixifor access to NVIDIA’s GPU debugging tools. These puzzles work exclusively on NVIDIA GPUs with CUDA support.

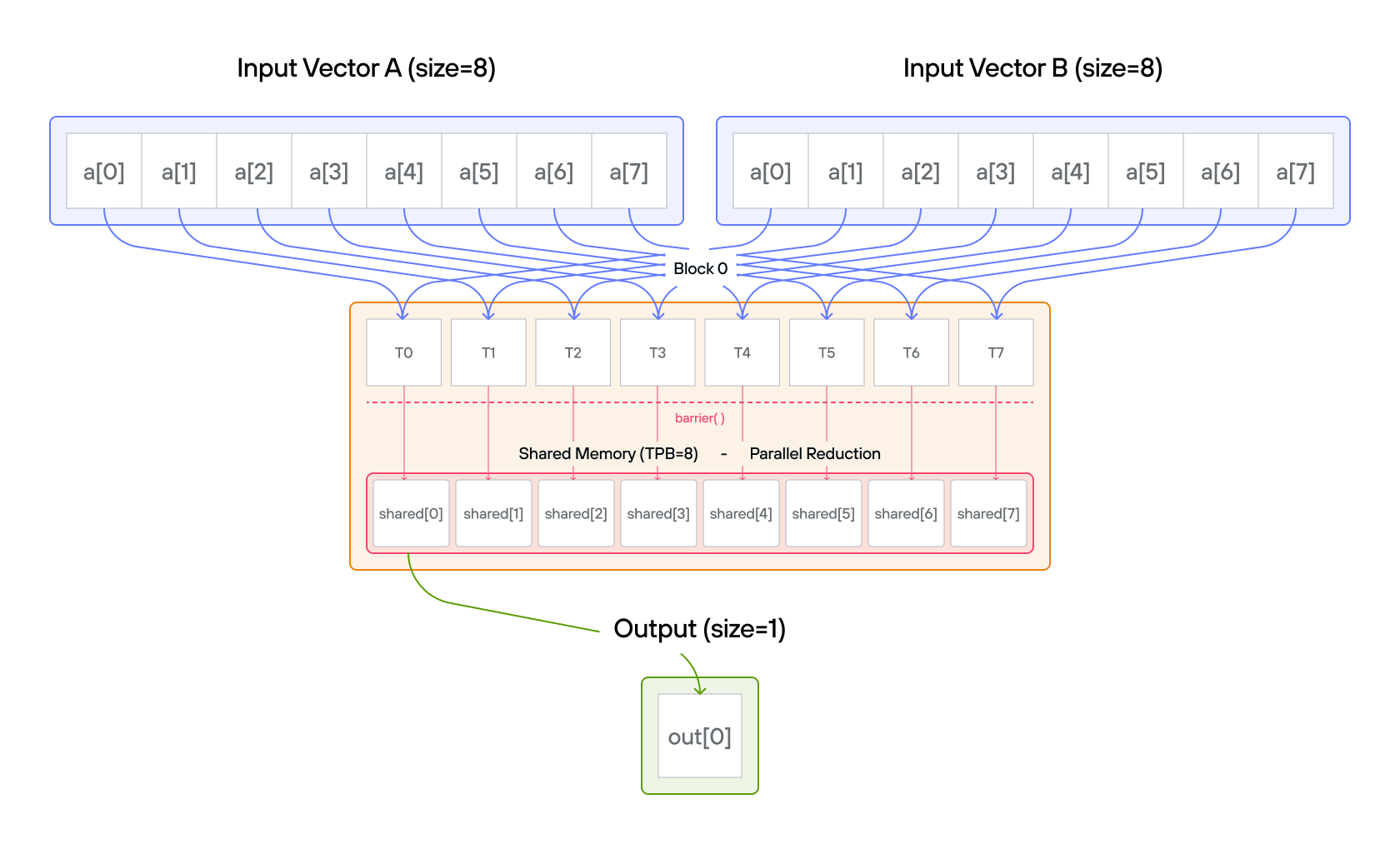

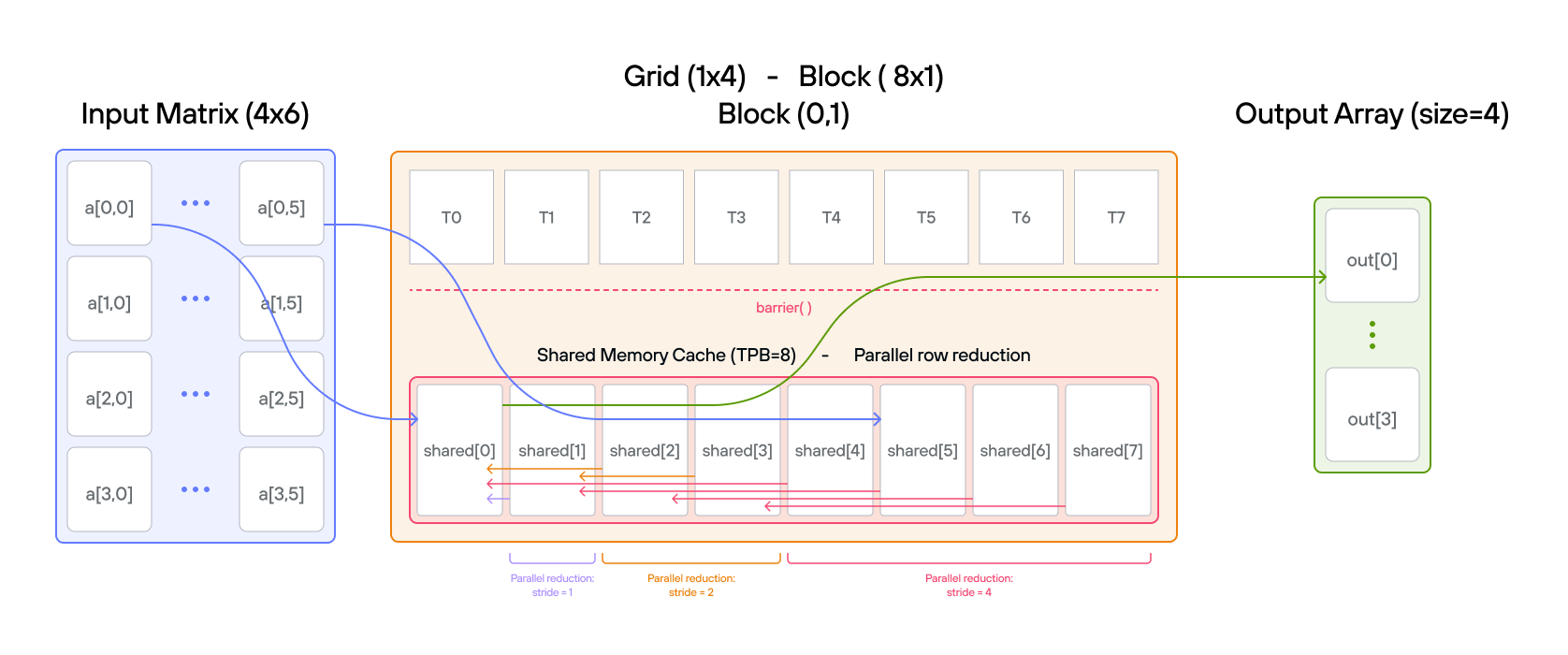

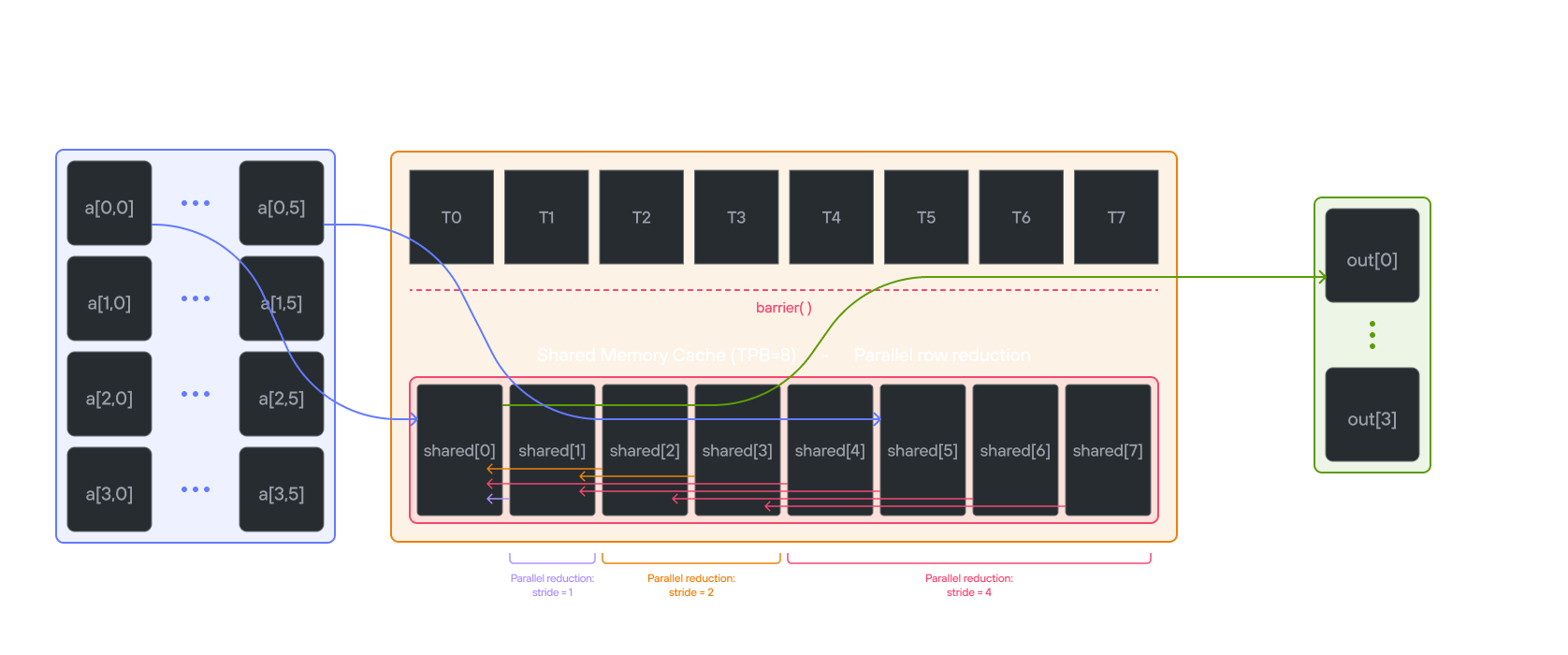

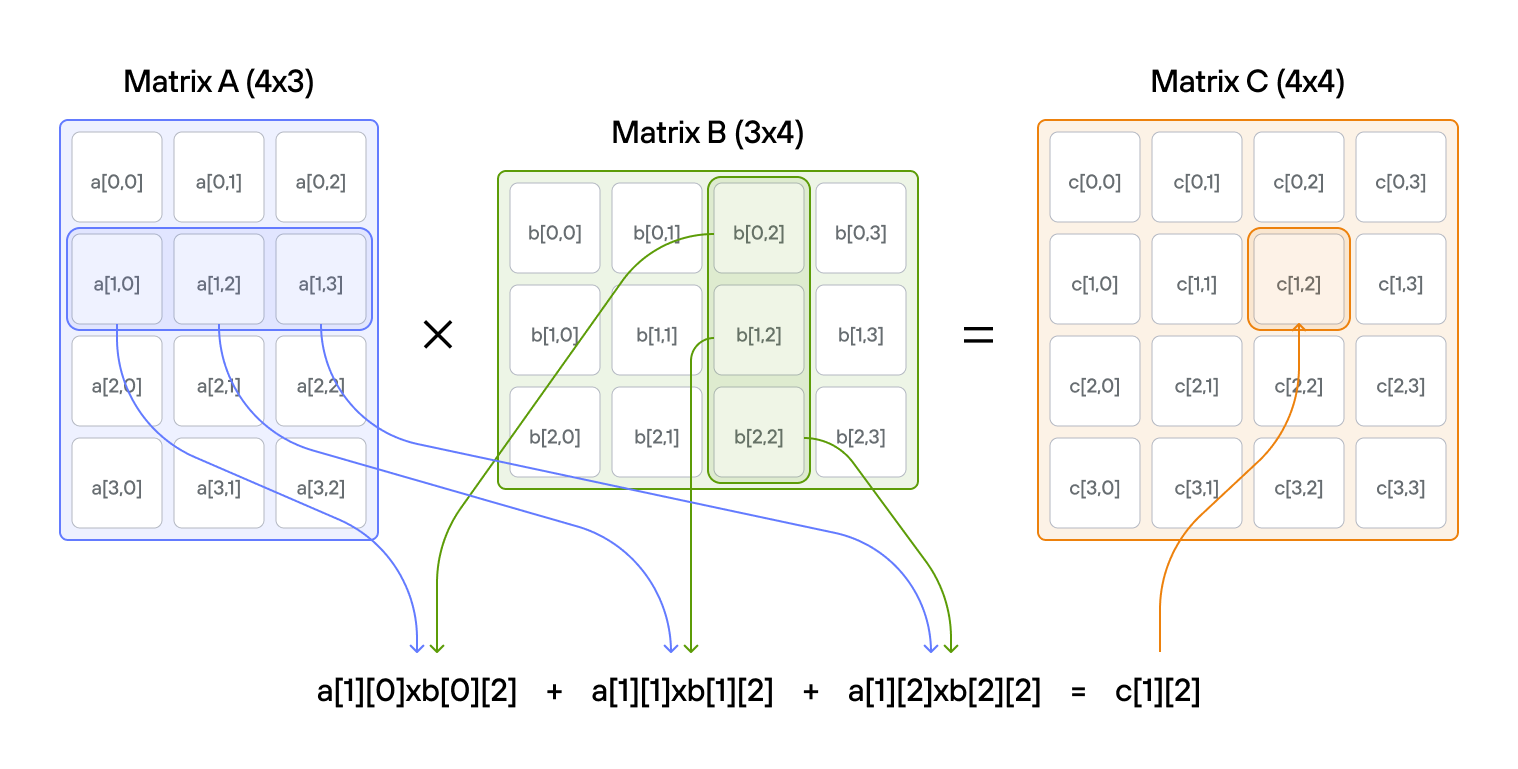

Part III: GPU algorithms (Puzzles 11-16) ✅

- Implement parallel reductions and pooling operations

- Build efficient convolution kernels

- Learn prefix sum (scan) algorithms

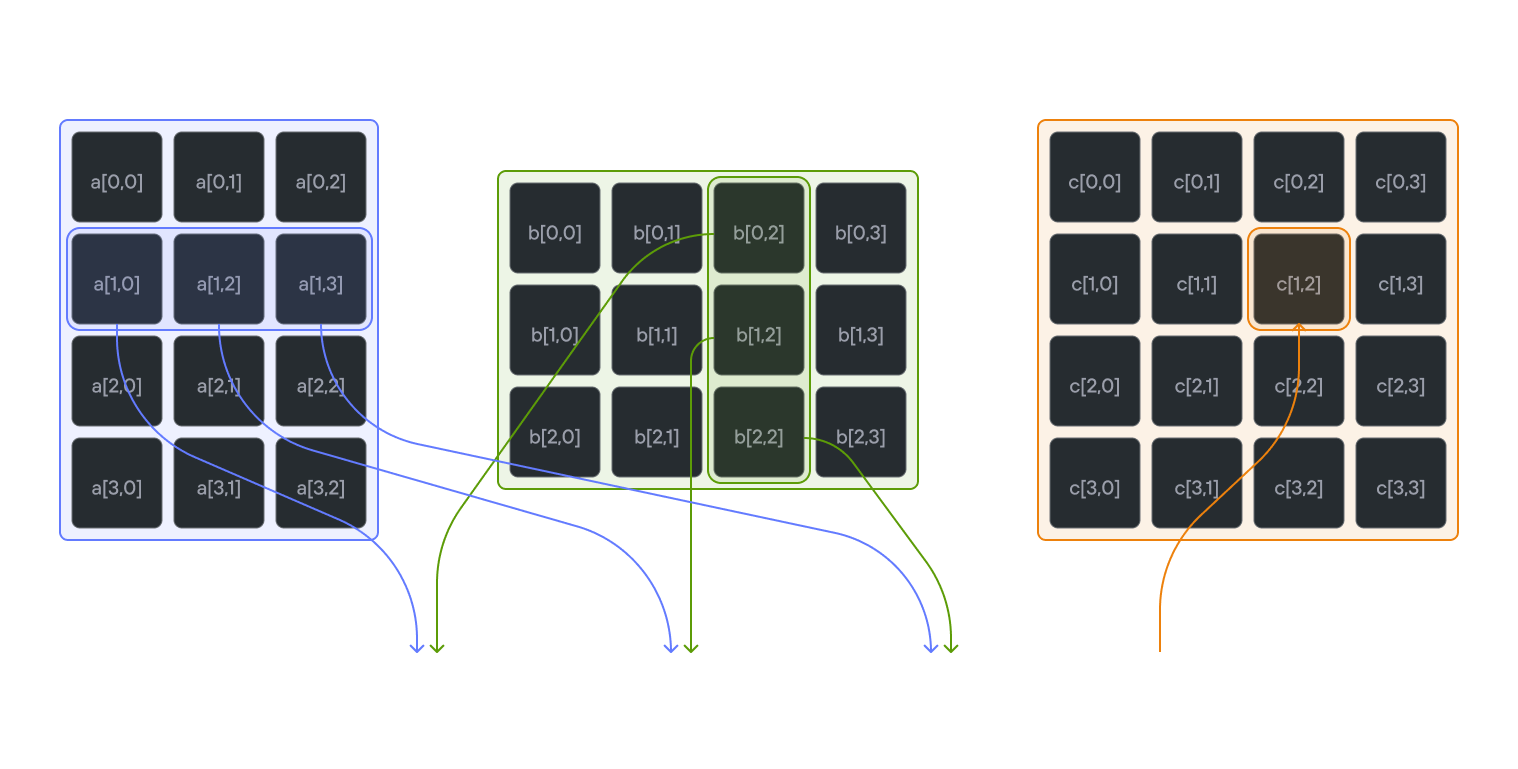

- Optimize matrix multiplication with tiling strategies

Part IV: MAX Graph integration (Puzzles 17-19) ✅

- Create custom MAX Graph operations

- Interface GPU kernels with Python code

- Build production-ready operations like softmax and attention

Part V: PyTorch integration (Puzzles 20-22) ✅

- Bridge Mojo GPU kernels with PyTorch tensors

- Use CustomOpLibrary for seamless tensor marshalling

- Integrate with torch.compile for optimized execution

- Learn kernel fusion and custom backward passes

Part VI: Mojo functional patterns & benchmarking (Puzzle 23) ✅

- Learn functional patterns: elementwise, tiled processing, vectorization

- Learn systematic performance optimization and trade-offs

- Develop quantitative benchmarking skills for performance analysis

- Understand GPU threading vs SIMD execution hierarchies

Part VII: Warp-level programming (Puzzles 24-26) ✅

- Learn warp fundamentals and SIMT execution models

- Learn essential warp operations: sum, shuffle_down, broadcast

- Implement advanced patterns with shuffle_xor and prefix_sum

- Combine warp programming with functional patterns effectively

Part VIII: Block-level programming (Puzzle 27) ✅

- Learn block-wide reductions with

block.sum()andblock.max() - Learn block-level prefix sum patterns and communication

- Implement efficient block.broadcast() for intra-block coordination

Part IX: Advanced memory systems (Puzzles 28-29) ✅

- Achieve optimal memory coalescing patterns

- Use async memory operations for overlapping compute with latency hiding

- Learn memory fences and synchronization primitives

- Learn prefetching and cache optimization strategies

Part X: Performance analysis & optimization (Puzzles 30-32) ✅

- Profile GPU kernels and identify bottlenecks

- Optimize occupancy and resource utilization

- Eliminate shared memory bank conflicts

Part XI: Advanced GPU features (Puzzles 33-34) ✅

- Program tensor cores for AI workloads

- Learn cluster programming in modern GPUs

The book uniquely challenges the status quo approach by first building understanding with low-level memory manipulation, then gradually transitioning to Mojo’s TileTensor abstractions. This provides both deep understanding of GPU memory patterns and practical knowledge of modern tensor-based approaches.

Ready to get started?

You now understand why GPU programming matters, why Mojo is suitable for this work, and how puzzle-based learning functions. You’re prepared to begin.

Next step: Head to How to Use This Book for setup instructions, system requirements, and guidance on running your first puzzle.

How to Use This Book

Each puzzle maintains a consistent structure to support systematic skill development:

- Overview: Problem definition and key concepts for each challenge

- Configuration: Technical setup and memory organization details

- Code to Complete: Implementation framework in

problems/pXX/with clearly marked sections to fill in - Tips: Strategic hints available when needed, without revealing complete solutions

- Solution: Comprehensive implementation analysis, including performance considerations and conceptual explanations

The puzzles increase in complexity systematically, building new concepts on established foundations. Working through them sequentially is recommended, as advanced puzzles assume familiarity with concepts from earlier challenges.

Running the code

All puzzles integrate with a testing framework that validates implementations against expected results. Each puzzle provides specific execution instructions and solution verification procedures.

Prerequisites

System requirements

Make sure your system meets our system requirements.

Compatible GPU

You’ll need a

compatible GPU to run the

puzzles. After setup, you can verify your GPU compatibility using the

gpu-specs command (see Quick Start section below).

Operating System

[!NOTE] Here is some documentation how to setup GPU support in your OS for

Windows WSL2 for Linux with NVIDIA

To setup NVIVIA GPU support on Windows Subsystem for Linux (WSL2) e.g. Unbuntu please follow the NVIDIA CUDA on WLS Guide.

The important information is to install the NVIDIA Windows CUDA Driver for Windows because they fully support WSL2. Once a Windows NVIDIA GPU driver is installed on the system, CUDA becomes available within WSL 2. The CUDA driver installed on Windows host will be stubbed inside the WSL 2 as libcuda.so, therefore users must not install any NVIDIA GPU Linux driver within WSL 2.

Once you have installed the drivers please test the installation

Verify from Windows: Open PowerShell (not WSL)

nvidia-smi

Verify from inside WSL: (first start WLS e.g. via wsl -d Ubuntu)

ls -l /usr/lib/wsl/lib/nvidia-smi

/usr/lib/wsl/lib/nvidia-smi

Check setup from Pixi optionally install missing requirements e.g. for cuda-gdb debugging

pixi run nvidia-smi

pixi run setup-cuda-gdb

pixi run mojo debug --help

pixi run cuda-gdb --version

For WSL you can install VSCode as your Editor

- Install VS Code on Windows from https://code.visualstudio.com/.

- Then install the Remote - WSL extension.

[!NOTE] All puzzles 1-15 are working on WSL and Linux.

Linux native with NVIDIA

Check GPU + Ubuntu version (Supported Ubuntu LTS: 20.04, 22.04, 24.04)

lspci | grep -i nvidia

lsb_release -a

Install NVIDIA driver (mandatory)

sudo ubuntu-drivers devices

sudo ubuntu-drivers autoinstall

sudo reboot

For Linux you can install VSCode as your Editor

- Install VS Code in Linux via VS Code APT repository

Import Microsoft GPG key

wget -qO- https://packages.microsoft.com/keys/microsoft.asc \

| gpg --dearmor \

| sudo tee /usr/share/keyrings/packages.microsoft.gpg > /dev/null

Add VS Code APT repository

echo "deb [arch=amd64 signed-by=/usr/share/keyrings/packages.microsoft.gpg] \

https://packages.microsoft.com/repos/code stable main" \

| sudo tee /etc/apt/sources.list.d/vscode.list

Install VS Code and verify installation

sudo apt update

sudo apt install code

code --version

[!NOTE] All puzzles 1-15 are working on Linux.

macOS Apple Silicon

For osx-arm64 users, you’ll need:

- macOS 15.0 or later for optimal compatibility. Run

pixi run check-macosand if it fails you’d need to upgrade. - Xcode 16 or later (minimum required). Use

xcodebuild -versionto check.

If xcrun -sdk macosx metal outputs

cannot execute tool 'metal' due to missing Metal toolchain proceed by running

xcodebuild -downloadComponent MetalToolchain

and then xcrun -sdk macosx metal, should give you the no input files error.

[!NOTE] Currently the puzzles 1-8 and 11-15 are working on macOS. We’re working to enable more. Please stay tuned!

Programming knowledge

Basic knowledge of:

- Programming fundamentals (variables, loops, conditionals, functions)

- Parallel computing concepts (threads, synchronization, race conditions)

- Basic familiarity with Mojo (language basics parts and intro to pointers section)

- GPU programming fundamentals is helpful!

No prior GPU programming experience is necessary! We’ll build that knowledge through the puzzles.

Let’s begin our journey into the exciting world of GPU computing with Mojo🔥!

Setting up your environment

-

Clone the GitHub repository and navigate to the repository:

# Clone the repository git clone https://github.com/modular/mojo-gpu-puzzles cd mojo-gpu-puzzles -

Install a package manager to run the Mojo🔥 programs:

Option 1 (Highly recommended)

pixi is the recommended option for this project because:

- Easy access to Modular’s MAX/Mojo packages

- Handles GPU dependencies

- Full conda + PyPI ecosystem support

> **Note: Some puzzles only work with `pixi`**

**Install:**

```bash

curl -fsSL https://pixi.sh/install.sh | sh

```

**Update:**

```bash

pixi self-update

```

Option 2: uv

**Install:**

```bash

curl -fsSL https://astral.sh/uv/install.sh | sh

```

**Update:**

```bash

uv self update

```

**Create a virtual environment:**

```bash

uv venv && source .venv/bin/activate

```

- Verify setup and run your first puzzle:

# Check your GPU specifications

pixi run gpu-specs

# Run your first puzzle

# This fails waiting for your implementation! follow the content

pixi run p01

# Check your GPU specifications

pixi run gpu-specs

# Run your first puzzle

# This fails waiting for your implementation! follow the content

pixi run -e amd p01

# Check your GPU specifications

pixi run gpu-specs

# Run your first puzzle

# This fails waiting for your implementation! follow the content

pixi run -e apple p01

# Install GPU-specific dependencies

uv pip install -e ".[nvidia]" # For NVIDIA GPUs

# OR

uv pip install -e ".[amd]" # For AMD GPUs

# Check your GPU specifications

uv run poe gpu-specs

# Run your first puzzle

# This fails waiting for your implementation! follow the content

uv run poe p01

Working with puzzles

Project structure

problems/: Where you implement your solutions (this is where you work!)solutions/: Reference solutions for comparison and learning that we use throughout the book

Workflow

- Navigate to

problems/pXX/to find the puzzle template - Implement your solution in the provided framework

- Test your implementation:

pixi run pXXoruv run poe pXX(remember to include your platform with-e platformsuch as-e amd) - Compare with

solutions/pXX/to learn different approaches

Essential commands

# Run puzzles (remember to include your platform with -e if needed)

pixi run pXX # NVIDIA (default) same as `pixi run -e nvidia pXX`

pixi run -e amd pXX # AMD GPU

pixi run -e apple pXX # Apple GPU

# Test solutions

pixi run tests # Test all solutions

pixi run tests pXX # Test specific puzzle

# Run manually

pixi run mojo problems/pXX/pXX.mojo # Your implementation

pixi run mojo solutions/pXX/pXX.mojo # Reference solution

# Interactive shell

pixi shell # Enter environment

mojo problems/p01/p01.mojo # Direct execution

exit # Leave shell

# Development

pixi run format # Format code

pixi task list # Available commands

# Note: uv is limited and some chapters require pixi

# Install GPU-specific dependencies:

uv pip install -e ".[nvidia]" # For NVIDIA GPUs

uv pip install -e ".[amd]" # For AMD GPUs

# Test solutions

uv run poe tests # Test all solutions

uv run poe tests pXX # Test specific puzzle

# Run manually

uv run mojo problems/pXX/pXX.mojo # Your implementation

uv run mojo solutions/pXX/pXX.mojo # Reference solution

GPU support matrix

The following table shows GPU platform compatibility for each puzzle. Different puzzles require different GPU features and vendor-specific tools.

| Puzzle | NVIDIA GPU | AMD GPU | Apple GPU | Notes |

|---|---|---|---|---|

| Part I: GPU Fundamentals | ||||

| 1 - Map | ✅ | ✅ | ✅ | Basic GPU kernels |

| 2 - Zip | ✅ | ✅ | ✅ | Basic GPU kernels |

| 3 - Guard | ✅ | ✅ | ✅ | Basic GPU kernels |

| 4 - Map 2D | ✅ | ✅ | ✅ | Basic GPU kernels |

| 5 - Broadcast | ✅ | ✅ | ✅ | Basic GPU kernels |

| 6 - Blocks | ✅ | ✅ | ✅ | Basic GPU kernels |

| 7 - Shared Memory | ✅ | ✅ | ✅ | Basic GPU kernels |

| 8 - Stencil | ✅ | ✅ | ✅ | Basic GPU kernels |

| Part II: Debugging | ||||

| 9 - GPU Debugger | ✅ | ❌ | ❌ | NVIDIA-specific debugging tools |

| 10 - Sanitizer | ✅ | ❌ | ❌ | NVIDIA-specific debugging tools |

| Part III: GPU Algorithms | ||||

| 11 - Reduction | ✅ | ✅ | ✅ | Basic GPU kernels |

| 12 - Scan | ✅ | ✅ | ✅ | Basic GPU kernels |

| 13 - Pool | ✅ | ✅ | ✅ | Basic GPU kernels |

| 14 - Conv | ✅ | ✅ | ✅ | Basic GPU kernels |

| 15 - Matmul | ✅ | ✅ | ✅ | Basic GPU kernels |

| 16 - Flashdot | ✅ | ✅ | ✅ | Advanced memory patterns |

| Part IV: MAX Graph | ||||

| 17 - Custom Op | ✅ | ✅ | ✅ | MAX Graph integration |

| 18 - Softmax | ✅ | ✅ | ✅ | MAX Graph integration |

| 19 - Attention | ✅ | ✅ | ✅ | MAX Graph integration |

| Part V: PyTorch Integration | ||||

| 20 - Torch Bridge | ✅ | ✅ | ❌ | PyTorch integration |

| 21 - Autograd | ✅ | ✅ | ❌ | PyTorch integration |

| 22 - Fusion | ✅ | ✅ | ❌ | PyTorch integration |

| Part VI: Functional Patterns | ||||

| 23 - Functional | ✅ | ✅ | ✅ | Advanced Mojo patterns |

| Part VII: Warp Programming | ||||

| 24 - Warp Sum | ✅ | ✅ | ✅ | Warp-level operations |

| 25 - Warp Communication | ✅ | ✅ | ✅ | Warp-level operations |

| 26 - Advanced Warp | ✅ | ✅ | ✅ | Warp-level operations |

| Part VIII: Block Programming | ||||

| 27 - Block Operations | ✅ | ✅ | ✅ | Block-level patterns |

| Part IX: Memory Systems | ||||

| 28 - Async Memory | ✅ | ✅ | ✅ | Advanced memory operations |

| 29 - Barriers | ✅ | ❌ | ❌ | Advanced NVIDIA-only synchronization |

| Part X: Performance Analysis | ||||

| 30 - Profiling | ✅ | ❌ | ❌ | NVIDIA profiling tools (NSight) |

| 31 - Occupancy | ✅ | ❌ | ❌ | NVIDIA profiling tools |

| 32 - Bank Conflicts | ✅ | ❌ | ❌ | NVIDIA profiling tools |

| Part XI: Modern GPU Features | ||||

| 33 - Tensor Cores | ✅ | ❌ | ❌ | NVIDIA Tensor Core specific |

| 34 - Cluster | ✅ | ❌ | ❌ | NVIDIA cluster programming |

Legend

- ✅ Supported: Puzzle works on this platform

- ❌ Not Supported: Puzzle requires platform-specific features

Platform notes

NVIDIA GPUs (Complete Support)

- All puzzles (1-34) work on NVIDIA GPUs with CUDA support

- Requires CUDA toolkit and compatible drivers

- Best learning experience with access to all features

AMD GPUs (Extensive Support)

- Most puzzles (1-8, 11-29) work with ROCm support

- Missing only: Debugging tools (9-10), profiling (30-32), Tensor Cores (33-34)

- Excellent for learning GPU programming including advanced algorithms and memory patterns

Apple GPUs (Basic Support)

- A selection of fundamental (1-8, 11-18) and advanced (23-27) puzzles are supported

- Missing: All advanced features, debugging, profiling tools

- Suitable for learning basic GPU programming patterns

Future Support: We’re actively working to expand tooling and platform support for AMD and Apple GPUs. Missing features like debugging tools, profiling capabilities, and advanced GPU operations are planned for future releases. Check back for updates as we continue to broaden cross-platform compatibility.

GPU Resources

Free cloud GPU platforms

If you don’t have local GPU access, several cloud platforms offer free GPU resources for learning and experimentation:

Google Colab

Google Colab provides free GPU access with some limitations for Mojo GPU programming:

Available GPUs:

- Tesla T4 (older Turing architecture)

- Tesla V100 (limited availability)

Limitations for Mojo GPU Puzzles:

- Older GPU architecture: T4 GPUs may have limited compatibility with advanced Mojo GPU features

- Session limits: 12-hour maximum runtime, then automatic disconnect

- Limited debugging support: NVIDIA debugging tools (puzzles 9-10) may not be fully available

- Package installation restrictions: May require workarounds for Mojo/MAX installation

- Performance limitations: Shared infrastructure affects consistent benchmarking

Recommended for: Basic GPU programming concepts (puzzles 1-8, 11-15) and learning fundamental patterns.

Kaggle Notebooks

Kaggle offers more generous free GPU access:

Available GPUs:

- Tesla T4 (30 hours per week free)

- P100 (limited availability)

Advantages over Colab:

- More generous time limits: 30 hours per week compared to Colab’s daily session limits

- Better persistence: Notebooks save automatically

- Consistent environment: More reliable package installation

Limitations for Mojo GPU Puzzles:

- Same GPU architecture constraints: T4 compatibility issues with advanced features

- Limited debugging tools: NVIDIA profiling and debugging tools (puzzles 9-10, 30-32) unavailable

- Mojo installation complexity: Requires manual setup of Mojo environment

- No cluster programming support: Advanced puzzles (33-34) won’t work

Recommended for: Extended learning sessions on fundamental GPU programming (puzzles 1-16).

Recommendations

- Complete Learning Path: Use NVIDIA GPU for full curriculum access (all 34 puzzles)

- Comprehensive Learning: AMD GPUs work well for most content (27 of 34 puzzles)

- Basic Understanding: Apple GPUs suitable for fundamental concepts (13 of 34 puzzles)

- Free Platform Learning: Google Colab/Kaggle suitable for basic to intermediate concepts (puzzles 1-16)

- Debugging & Profiling: NVIDIA GPU required for debugging tools and performance analysis

- Modern GPU Features: NVIDIA GPU required for Tensor Cores and cluster programming

Development

Please see details in the README.

Join the community

Join our vibrant community to discuss GPU programming, share solutions, and get help!

🏆 Claim Your Rewards

Have you completed the available puzzles? We’re giving away free sticker packs to celebrate your achievement!

To claim your free stickers:

- Fork the GitHub repository https://github.com/modular/mojo-gpu-puzzles

- Add your solutions to the available puzzles

- Submit your solutions through this form and we’ll send you exclusive Modular stickers!

Currently, we can ship stickers to addresses within North America. If you’re located elsewhere, please still submit your solutions – we’re working on expanding our shipping reach and would love to recognize your achievements when possible.

Puzzle 1: Map

Overview

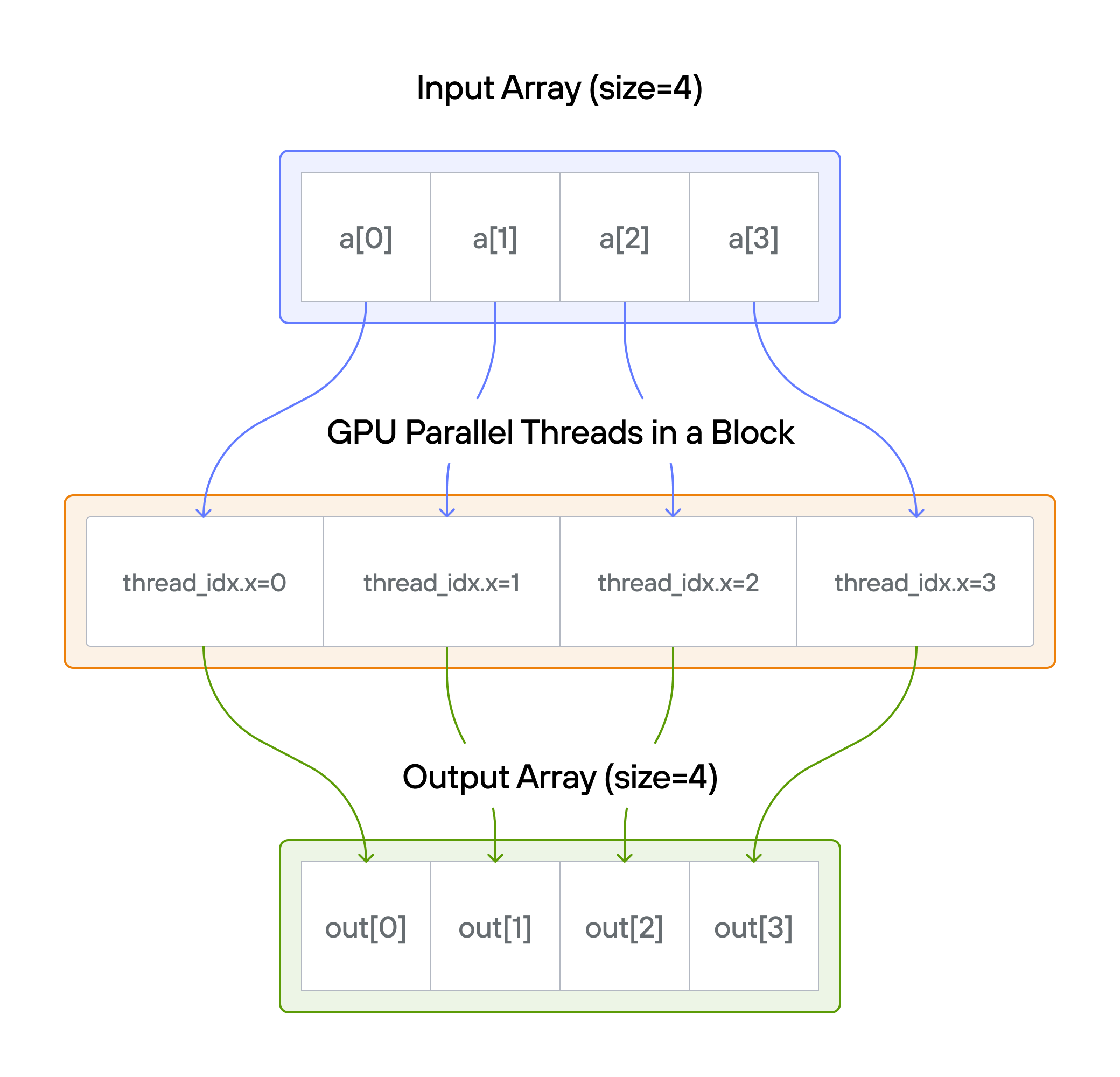

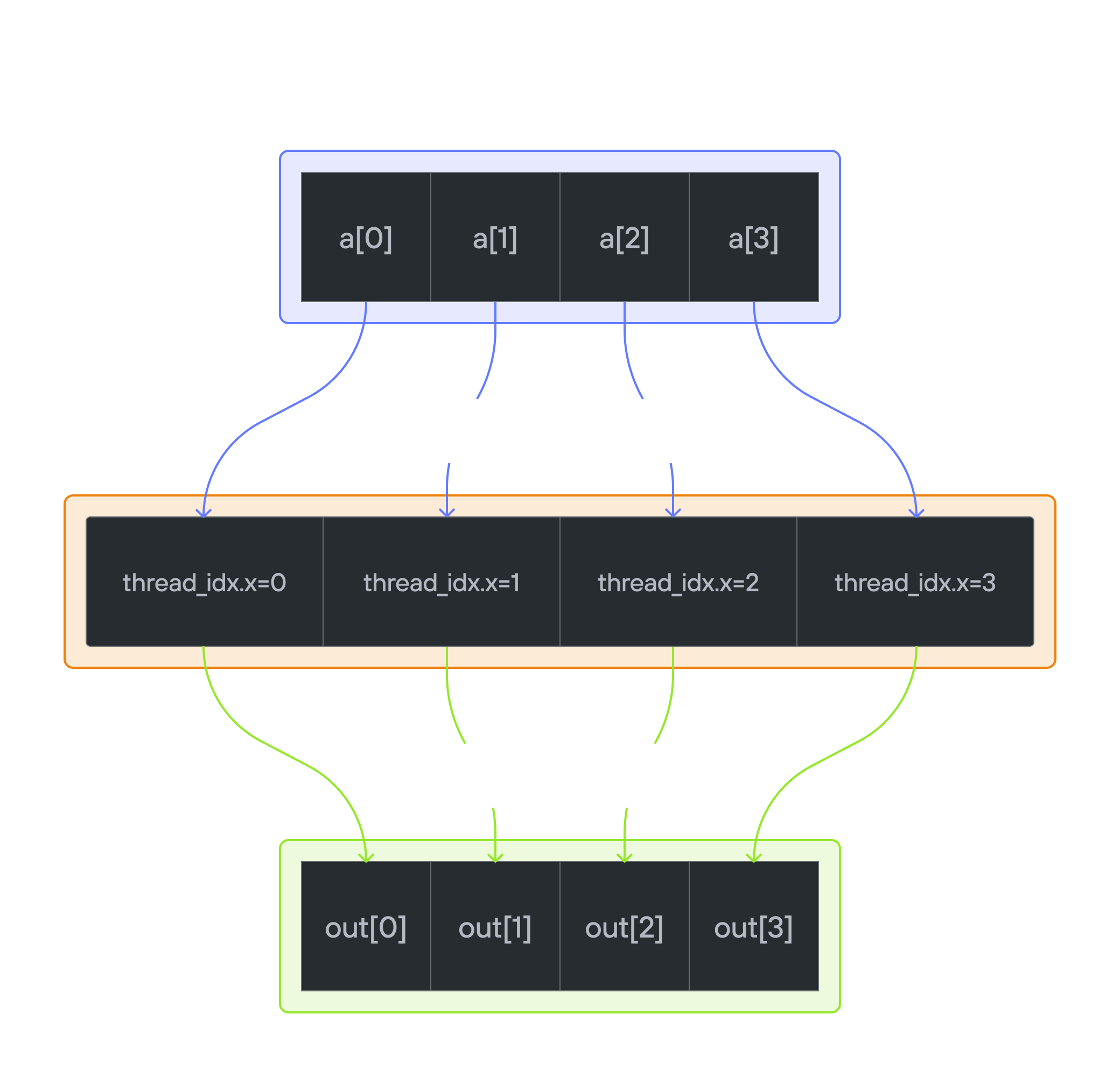

This puzzle introduces the fundamental concept of GPU parallelism: mapping

individual threads to data elements for concurrent processing. Your task is to

implement a kernel that adds 10 to each element of vector a, storing the

results in vector output.

Note: You have 1 thread per position.

Key concepts

- Basic GPU kernel structure

- One-to-one thread to data mapping

- Memory access patterns

- Array operations on GPU

For each position \(i\): \[\Large output[i] = a[i] + 10\]

What we cover

🔰 Raw Memory Approach

Start with direct memory manipulation to understand GPU fundamentals.

💡 Preview: Modern Approach with TileTensor

See how TileTensor simplifies GPU programming with safer, cleaner code.

💡 Tip: Understanding both approaches leads to better appreciation of modern GPU programming patterns.

Key concepts

In this puzzle, you’ll learn about:

-

Basic GPU kernel structure

-

Thread indexing with

thread_idx.x -

Simple parallel operations

-

Parallelism: Each thread executes independently

-

Thread indexing: Access element at position

i = thread_idx.x -

Memory access: Read from

a[i]and write tooutput[i] -

Data independence: Each output depends only on its corresponding input

Code to complete

comptime SIZE = 4

comptime BLOCKS_PER_GRID = 1

comptime THREADS_PER_BLOCK = SIZE

comptime dtype = DType.float32

def add_10(

output: UnsafePointer[Scalar[dtype], MutAnyOrigin],

a: UnsafePointer[Scalar[dtype], MutAnyOrigin],

):

var i = thread_idx.x

# FILL ME IN (roughly 1 line)

View full file: problems/p01/p01.mojo

Tips

- Store

thread_idx.xini - Add 10 to

a[i] - Store result in

output[i]

Running the code

To test your solution, run the following command in your terminal:

pixi run p01

pixi run -e amd p01

pixi run -e apple p01

uv run poe p01

Your output will look like this if the puzzle isn’t solved yet:

out: HostBuffer([0.0, 0.0, 0.0, 0.0])

expected: HostBuffer([10.0, 11.0, 12.0, 13.0])

Solution

def add_10(

output: UnsafePointer[Scalar[dtype], MutAnyOrigin],

a: UnsafePointer[Scalar[dtype], MutAnyOrigin],

):

var i = thread_idx.x

output[i] = a[i] + 10.0

This solution:

- Gets thread index with

i = thread_idx.x - Adds 10 to input value:

output[i] = a[i] + 10.0

Why consider TileTensor?

Looking at our traditional implementation below, you might notice some potential issues:

Current approach

i = thread_idx.x

output[i] = a[i] + 10.0

This works for 1D arrays, but what happens when we need to:

- Handle 2D or 3D data?

- Deal with different memory layouts?

- Ensure coalesced memory access?

Preview of future challenges

As we progress through the puzzles, array indexing will become more complex:

# 2D indexing coming in later puzzles

idx = row * WIDTH + col

# 3D indexing

idx = (batch * HEIGHT + row) * WIDTH + col

# With padding

idx = (batch * padded_height + row) * padded_width + col

TileTensor preview

TileTensor will help us handle these cases more elegantly:

# Future preview - don't worry about this syntax yet!

output[i, j] = a[i, j] + 10.0 # 2D indexing

output[b, i, j] = a[b, i, j] + 10.0 # 3D indexing

We’ll learn about TileTensor in detail in Puzzle 4, where these concepts become essential. For now, focus on understanding:

- Basic thread indexing

- Simple memory access patterns

- One-to-one mapping of threads to data

💡 Key Takeaway: While direct indexing works for simple cases, we’ll soon need more sophisticated tools for complex GPU programming patterns.

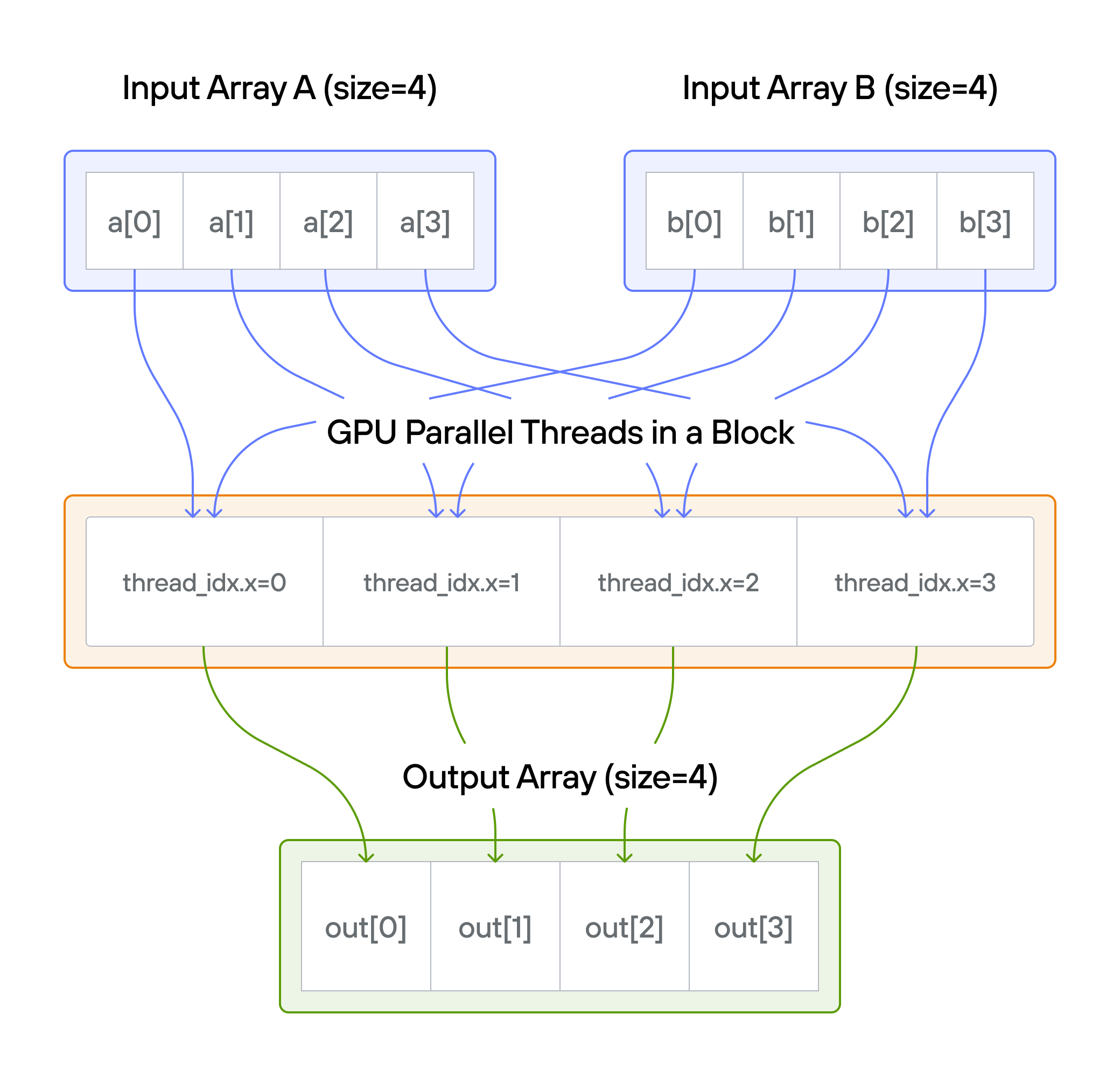

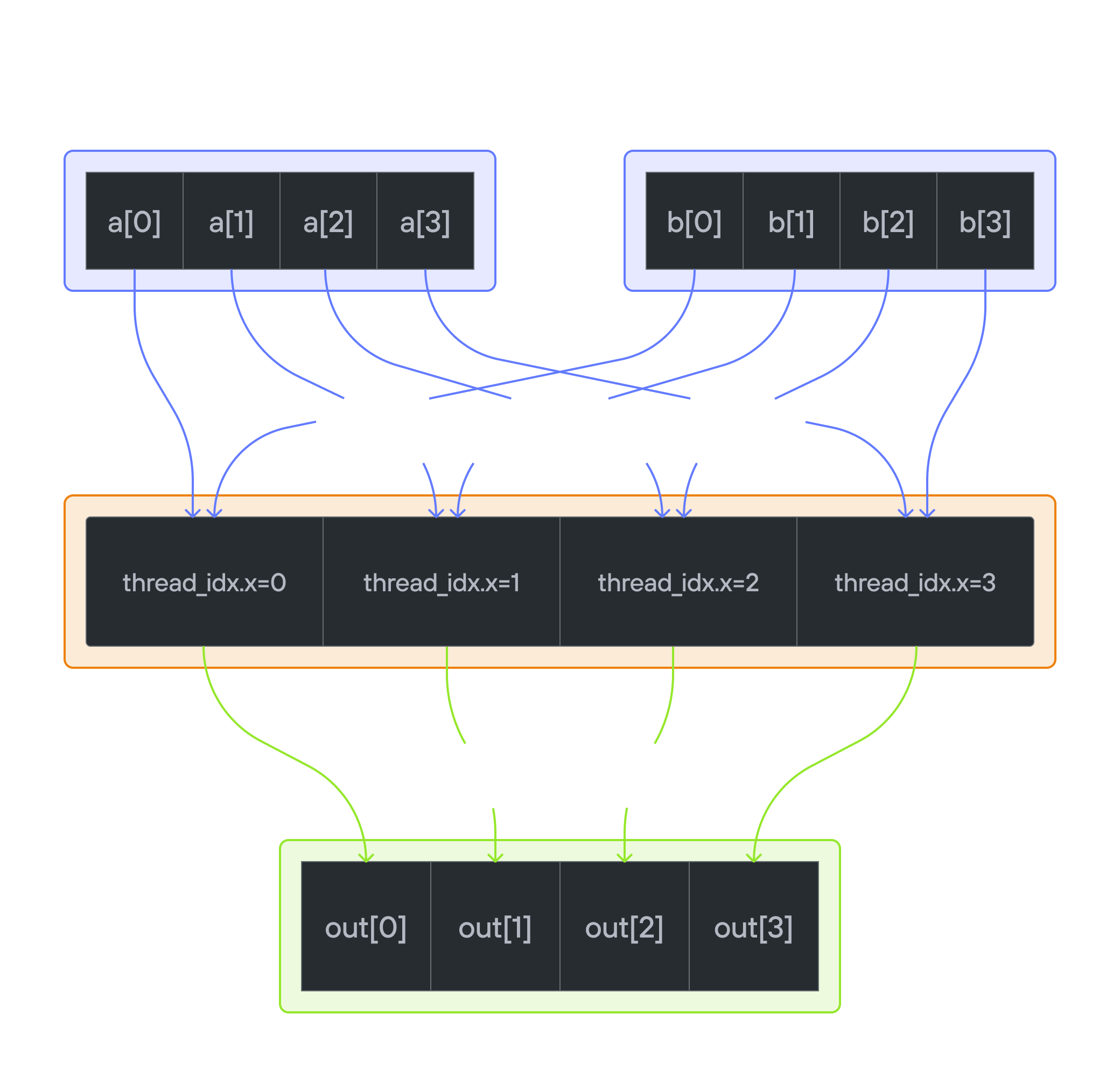

Puzzle 2: Zip

Overview

Implement a kernel that adds together each position of vector a and vector b

and stores it in output.

Note: You have 1 thread per position.

Key concepts

In this puzzle, you’ll learn about:

- Processing multiple input arrays in parallel

- Element-wise operations with multiple inputs

- Thread-to-data mapping across arrays

- Memory access patterns with multiple arrays

For each thread \(i\): \[\Large output[i] = a[i] + b[i]\]

Memory access pattern

Thread 0: a[0] + b[0] → output[0]

Thread 1: a[1] + b[1] → output[1]

Thread 2: a[2] + b[2] → output[2]

...

💡 Note: Notice how we’re now managing three arrays (a, b, output) in

our kernel. As we progress to more complex operations, managing multiple array

accesses will become increasingly challenging.

Code to complete

comptime SIZE = 4

comptime BLOCKS_PER_GRID = 1

comptime THREADS_PER_BLOCK = SIZE

comptime dtype = DType.float32

def add(

output: UnsafePointer[Scalar[dtype], MutAnyOrigin],

a: UnsafePointer[Scalar[dtype], MutAnyOrigin],

b: UnsafePointer[Scalar[dtype], MutAnyOrigin],

):

var i = thread_idx.x

# FILL ME IN (roughly 1 line)

View full file: problems/p02/p02.mojo

Tips

- Store

thread_idx.xini - Add

a[i]andb[i] - Store result in

output[i]

Running the code

To test your solution, run the following command in your terminal:

pixi run p02

pixi run -e amd p02

pixi run -e apple p02

uv run poe p02

Your output will look like this if the puzzle isn’t solved yet:

out: HostBuffer([0.0, 0.0, 0.0, 0.0])

expected: HostBuffer([0.0, 2.0, 4.0, 6.0])

Solution

def add(

output: UnsafePointer[Scalar[dtype], MutAnyOrigin],

a: UnsafePointer[Scalar[dtype], MutAnyOrigin],

b: UnsafePointer[Scalar[dtype], MutAnyOrigin],

):

var i = thread_idx.x

output[i] = a[i] + b[i]

This solution:

- Gets thread index with

i = thread_idx.x - Adds values from both arrays:

output[i] = a[i] + b[i]

Looking ahead

While this direct indexing works for simple element-wise operations, consider:

- What if arrays have different layouts?

- What if we need to broadcast one array to another?

- How to ensure coalesced access across multiple arrays?

These questions will be addressed when we introduce TileTensor in Puzzle 4.

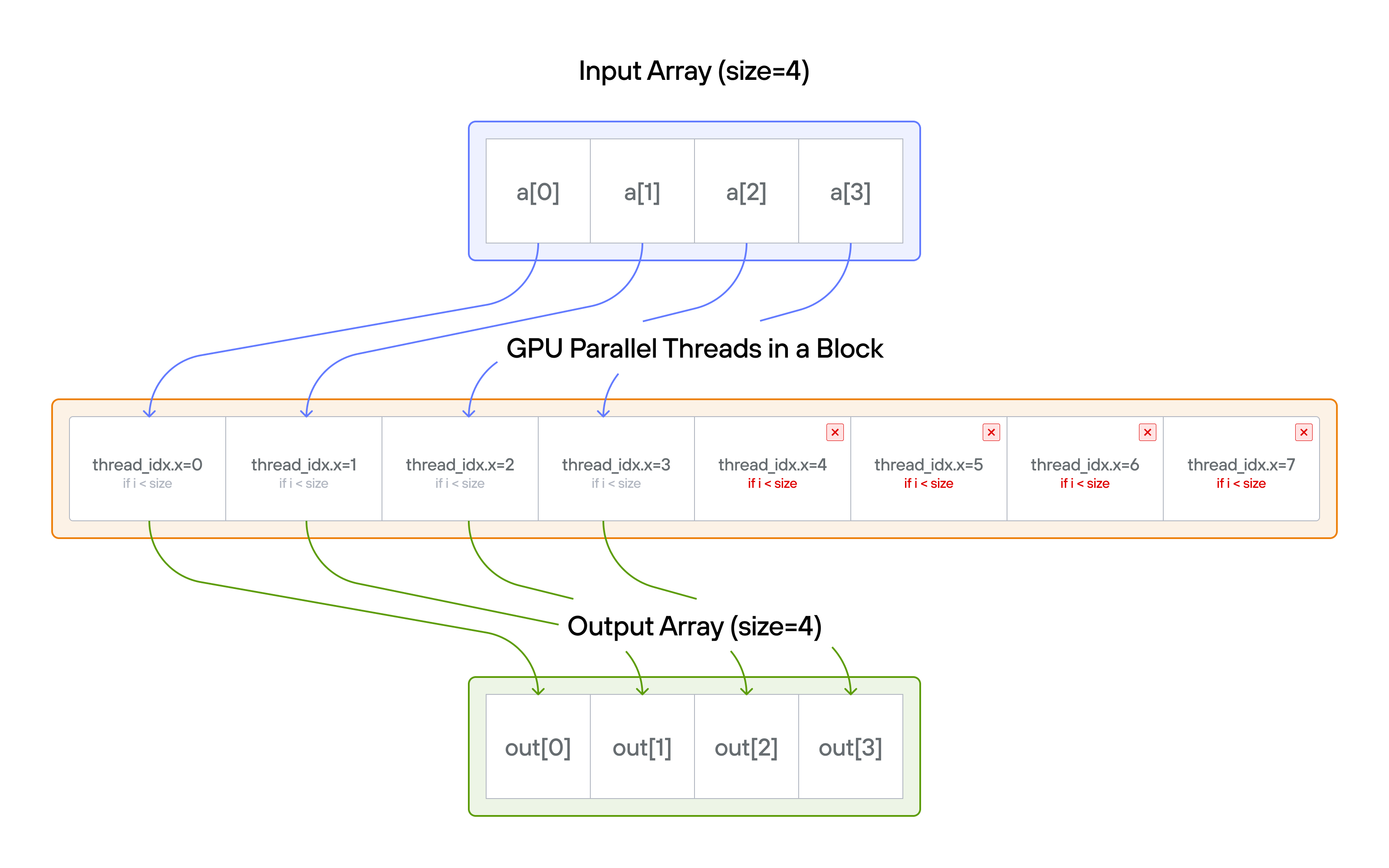

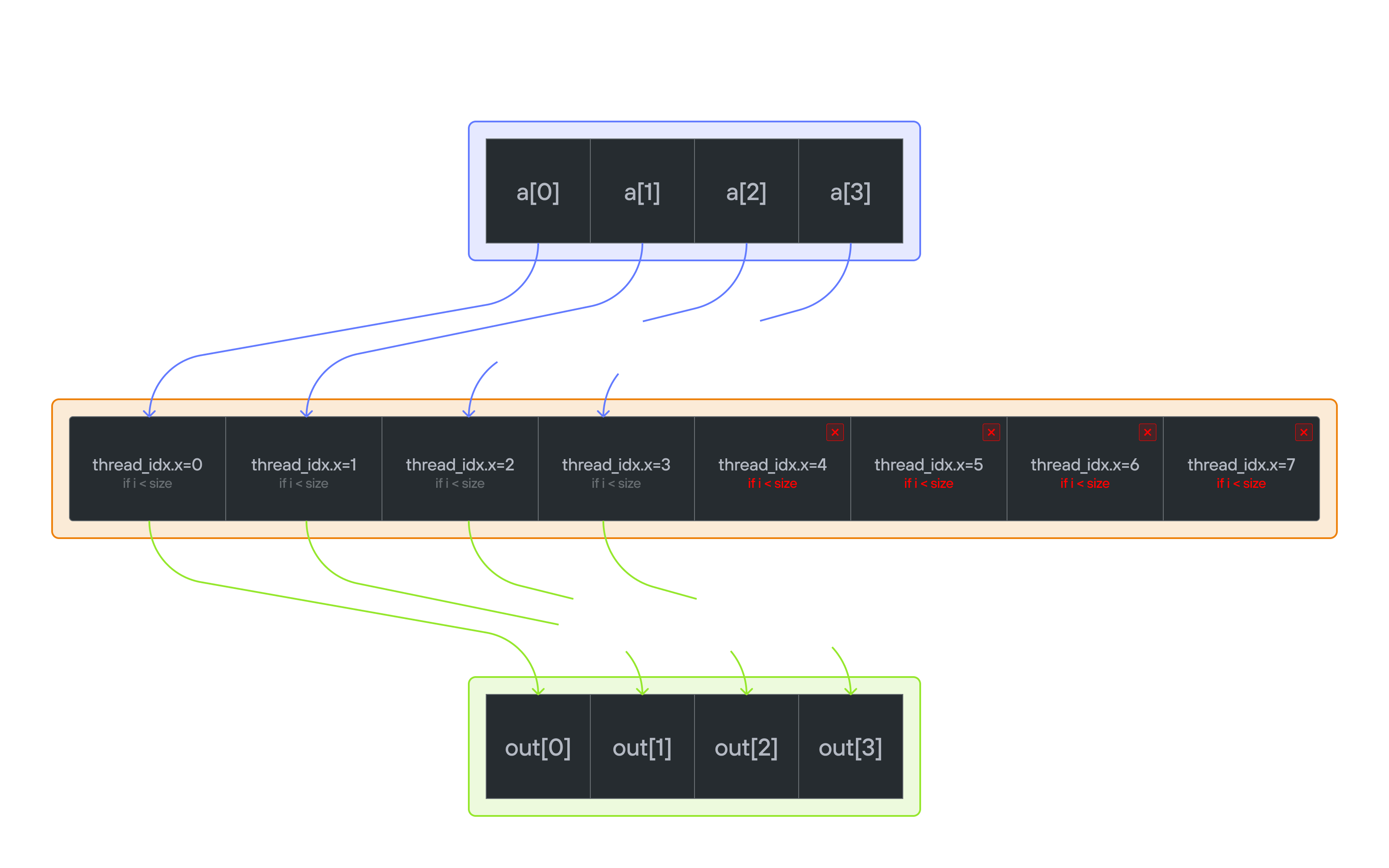

Puzzle 3: Guards

Overview

Implement a kernel that adds 10 to each position of vector a and stores it in

vector output.

Note: You have more threads than positions. This means you need to protect against out-of-bounds memory access.

Key concepts

This puzzle covers:

- Handling thread/data size mismatches

- Preventing out-of-bounds memory access

- Using conditional execution in GPU kernels

- Safe memory access patterns

Mathematical description

For each thread \(i\): \[\Large \text{if}\ i < \text{size}: output[i] = a[i] + 10\]

Memory safety pattern

Thread 0 (i=0): if 0 < size: output[0] = a[0] + 10 ✓ Valid

Thread 1 (i=1): if 1 < size: output[1] = a[1] + 10 ✓ Valid

Thread 2 (i=2): if 2 < size: output[2] = a[2] + 10 ✓ Valid

Thread 3 (i=3): if 3 < size: output[3] = a[3] + 10 ✓ Valid

Thread 4 (i=4): if 4 < size: ❌ Skip (out of bounds)

Thread 5 (i=5): if 5 < size: ❌ Skip (out of bounds)

💡 Note: Boundary checking becomes increasingly complex with:

- Multi-dimensional arrays

- Different array shapes

- Complex access patterns

Code to complete

comptime SIZE = 4

comptime BLOCKS_PER_GRID = 1

comptime THREADS_PER_BLOCK = 8

comptime dtype = DType.float32

def add_10_guard(

output: UnsafePointer[Scalar[dtype], MutAnyOrigin],

a: UnsafePointer[Scalar[dtype], MutAnyOrigin],

size: Int,

):

var i = thread_idx.x

# FILL ME IN (roughly 2 lines)

View full file: problems/p03/p03.mojo

Tips

- Store

thread_idx.xini - Add guard:

if i < size - Inside guard:

output[i] = a[i] + 10.0

Running the code

To test your solution, run the following command in your terminal:

pixi run p03

pixi run -e amd p03

pixi run -e apple p03

uv run poe p03

Your output will look like this if the puzzle isn’t solved yet:

out: HostBuffer([0.0, 0.0, 0.0, 0.0])

expected: HostBuffer([10.0, 11.0, 12.0, 13.0])

Solution

def add_10_guard(

output: UnsafePointer[Scalar[dtype], MutAnyOrigin],

a: UnsafePointer[Scalar[dtype], MutAnyOrigin],

size: Int,

):

var i = thread_idx.x

if i < size:

output[i] = a[i] + 10.0

This solution:

- Gets thread index with

i = thread_idx.x - Guards against out-of-bounds access with

if i < size - Inside guard: adds 10 to input value

You might wonder why it passes the test even without the bound-check! Always remember that passing the tests doesn’t necessarily mean the code is sound and free of Undefined Behaviors. In puzzle 10 we’ll examine such cases and use some tools to catch such soundness bugs.

Looking ahead

While simple boundary checks work here, consider these challenges:

- What about 2D/3D array boundaries?

- How to handle different shapes efficiently?

- What if we need padding or edge handling?

Example of growing complexity:

# Current: 1D bounds check

if i < size: ...

# Coming soon: 2D bounds check

if i < height and j < width: ...

# Later: 3D with padding

if i < height and j < width and k < depth and

i >= padding and j >= padding: ...

These boundary handling patterns will become more elegant when we learn about TileTensor in Puzzle 4, which provides built-in shape management.

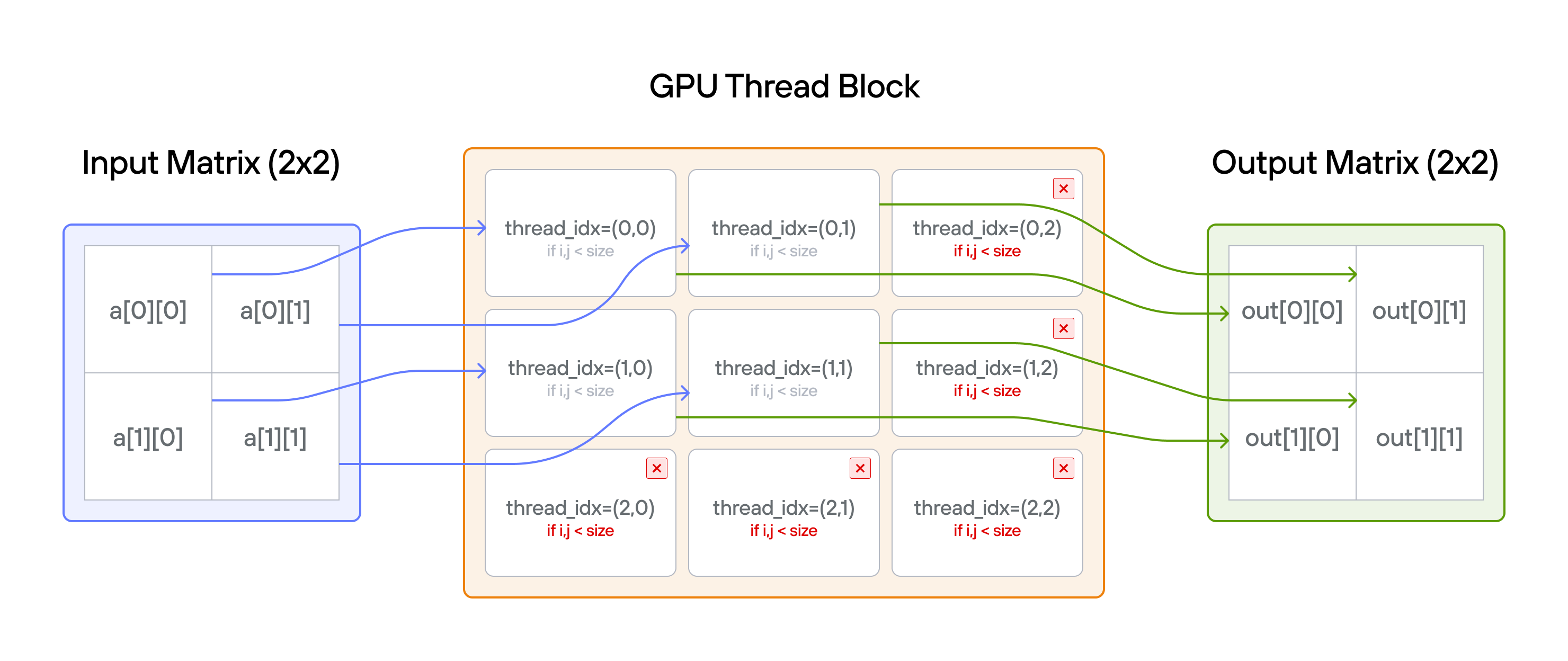

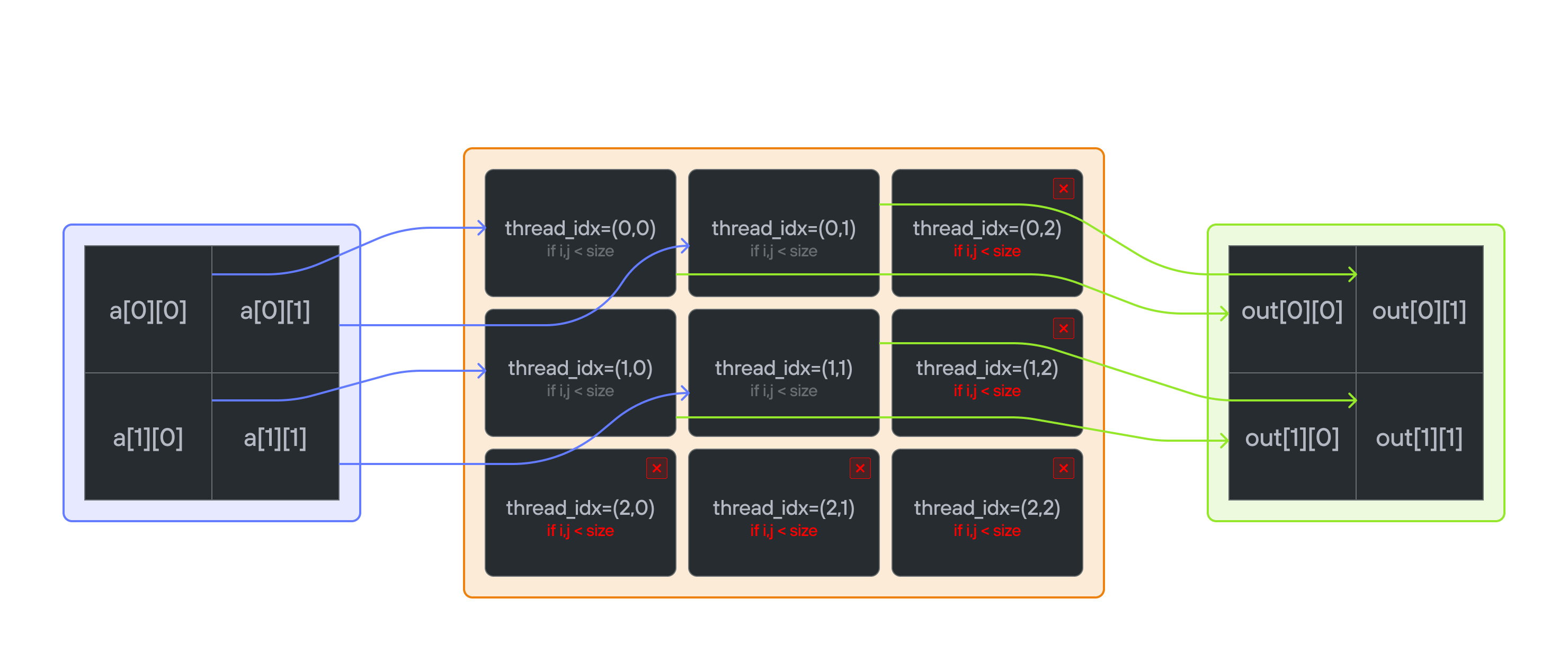

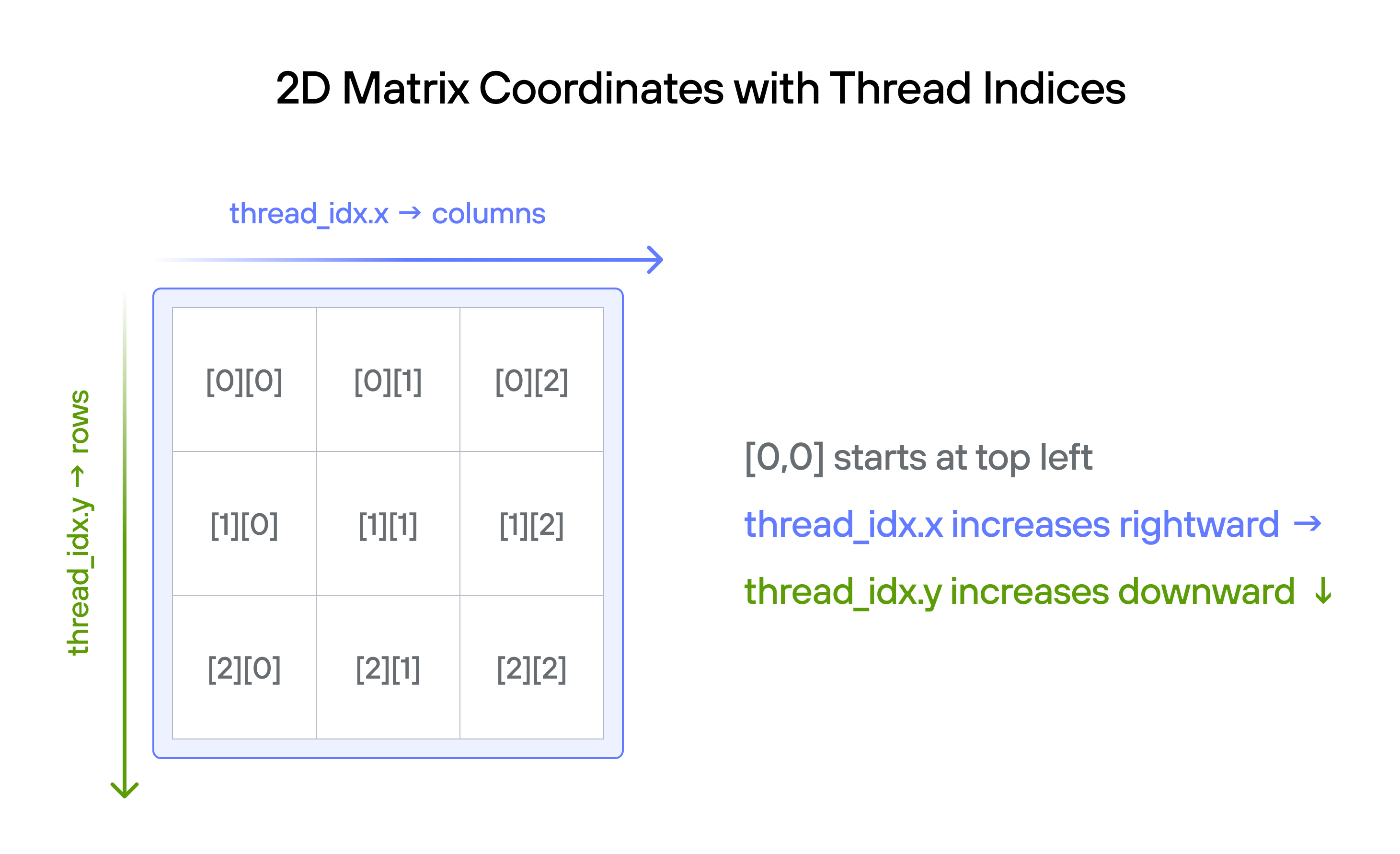

Puzzle 4: 2D Map

Overview

Implement a kernel that adds 10 to each position of 2D square matrix a and

stores it in 2D square matrix output.

Note: You have more threads than positions.

Key concepts

- 2D thread indexing

- Matrix operations on GPU

- Handling excess threads

- Memory layout patterns

For each position \((i,j)\): \[\Large output[i,j] = a[i,j] + 10\]

Thread indexing convention

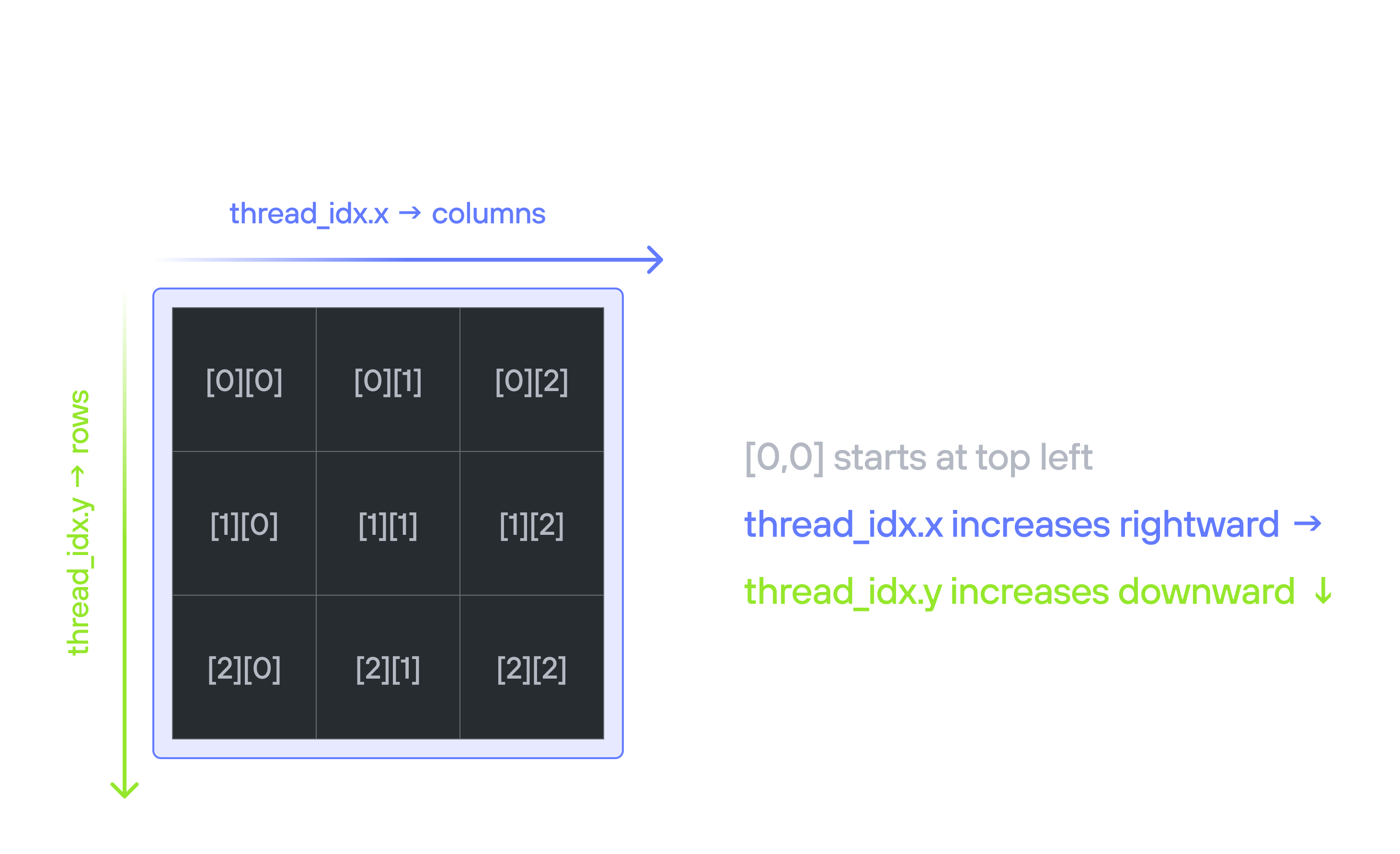

When working with 2D matrices in GPU programming, we follow a natural mapping between thread indices and matrix coordinates:

thread_idx.ycorresponds to the row indexthread_idx.xcorresponds to the column index

This convention aligns with:

- The standard mathematical notation where matrix positions are specified as (row, column)

- The visual representation of matrices where rows go top-to-bottom (y-axis) and columns go left-to-right (x-axis)

- Common GPU programming patterns where thread blocks are organized in a 2D grid matching the matrix structure

Historical origins

While graphics and image processing typically use \((x,y)\) coordinates, matrix operations in computing have historically used (row, column) indexing. This comes from how early computers stored and processed 2D data: line by line, top to bottom, with each line read left to right. This row-major memory layout proved efficient for both CPUs and GPUs, as it matches how they access memory sequentially. When GPU programming adopted thread blocks for parallel processing, it was natural to map

thread_idx.yto rows andthread_idx.xto columns, maintaining consistency with established matrix indexing conventions.

Implementation approaches

🔰 Raw memory approach

Learn how 2D indexing works with manual memory management.

📚 Learn about TileTensor

Discover a powerful abstraction that simplifies multi-dimensional array operations and memory management on GPU.

🚀 Modern 2D operations

Put TileTensor into practice with natural 2D indexing and automatic bounds checking.

💡 Note: From this puzzle onward, we’ll primarily use TileTensor for cleaner, safer GPU code.

Overview

Implement a kernel that adds 10 to each position of 2D square matrix a and

stores it in 2D square matrix output.

Note: You have more threads than positions.

Key concepts

In this puzzle, you’ll learn about:

- Working with 2D thread indices (

thread_idx.x,thread_idx.y) - Converting 2D coordinates to 1D memory indices

- Handling boundary checks in two dimensions

The key insight is understanding how to map from 2D thread coordinates \((i,j)\) to elements in a row-major matrix of size \(n \times n\), while ensuring thread indices are within bounds.

- 2D indexing: Each thread has a unique \((i,j)\) position

- Memory layout: Row-major ordering maps 2D to 1D memory

- Guard condition: Need bounds checking in both dimensions

- Thread bounds: More threads \((3 \times 3)\) than matrix elements \((2 \times 2)\)

Code to complete

comptime SIZE = 2

comptime BLOCKS_PER_GRID = 1

comptime THREADS_PER_BLOCK = (3, 3)

comptime dtype = DType.float32

def add_10_2d(

output: UnsafePointer[Scalar[dtype], MutAnyOrigin],

a: UnsafePointer[Scalar[dtype], MutAnyOrigin],

size: Int,

):

var row = thread_idx.y

var col = thread_idx.x

# FILL ME IN (roughly 2 lines)

View full file: problems/p04/p04.mojo

Tips

- Get 2D indices:

row = thread_idx.y,col = thread_idx.x - Add guard:

if row < size and col < size - Inside guard add 10 in row-major way!

Running the code

To test your solution, run the following command in your terminal:

pixi run p04

pixi run -e amd p04

pixi run -e apple p04

uv run poe p04

Your output will look like this if the puzzle isn’t solved yet:

out: HostBuffer([0.0, 0.0, 0.0, 0.0])

expected: HostBuffer([10.0, 11.0, 12.0, 13.0])

Solution

def add_10_2d(

output: UnsafePointer[Scalar[dtype], MutAnyOrigin],

a: UnsafePointer[Scalar[dtype], MutAnyOrigin],

size: Int,

):

var row = thread_idx.y

var col = thread_idx.x

if row < size and col < size:

output[row * size + col] = a[row * size + col] + 10.0

This solution:

- Get 2D indices:

row = thread_idx.y,col = thread_idx.x - Add guard:

if row < size and col < size - Inside guard:

output[row * size + col] = a[row * size + col] + 10.0

Introduction to TileTensor

Let’s take a quick break from solving puzzles to preview a powerful abstraction that will make our GPU programming journey more enjoyable: 🥁… the TileTensor.

💡 This is a motivational overview of TileTensor’s capabilities. Don’t worry about understanding everything now - we’ll explore each feature in depth as we progress through the puzzles.

The challenge: Growing complexity

Let’s look at the challenges we’ve faced so far:

# Puzzle 1: Simple indexing

output[i] = a[i] + 10.0

# Puzzle 2: Multiple array management

output[i] = a[i] + b[i]

# Puzzle 3: Bounds checking

if i < size:

output[i] = a[i] + 10.0

As dimensions grow, code becomes more complex:

# Traditional 2D indexing for row-major 2D matrix

idx = row * WIDTH + col

if row < height and col < width:

output[idx] = a[idx] + 10.0

The solution: A peek at TileTensor

TileTensor will help us tackle these challenges with elegant solutions. Here’s a glimpse of what’s coming:

- Natural Indexing: Use

tensor[i, j]instead of manual offset calculations - Flexible Memory Layouts: Support for row-major, column-major, and tiled organizations

- Performance Optimization: Efficient memory access patterns for GPU

A taste of what’s ahead

Let’s look at a few examples of what TileTensor can do. Don’t worry about understanding all the details now - we’ll cover each feature thoroughly in upcoming puzzles.

Basic usage example

from layout import TileTensor

from layout.tile_layout import row_major

# Define layout

comptime HEIGHT = 2

comptime WIDTH = 3

comptime layout = row_major[HEIGHT, WIDTH]()

comptime LayoutType = type_of(layout)

# Create tensor

tensor = TileTensor(buffer, layout)

# Access elements naturally

tensor[0, 0] = 1.0 # First element

tensor[1, 2] = 2.0 # Last element

To learn more about Layout and TileTensor, see these guides from the

Mojo manual

Quick example

Let’s put everything together with a simple example that demonstrates the basics of TileTensor:

# ===----------------------------------------------------------------------=== #

#

# This file is Modular Inc proprietary.

#

# ===----------------------------------------------------------------------=== #

from std.gpu.host import DeviceContext

from layout import TileTensor

from layout.tile_layout import row_major

comptime HEIGHT = 2

comptime WIDTH = 3

comptime dtype = DType.float32

comptime layout = row_major[HEIGHT, WIDTH]()

comptime LayoutType = type_of(layout)

def kernel(

tensor: TileTensor[mut=True, dtype, LayoutType, MutAnyOrigin],

):

print("Before:")

print(tensor)

tensor[0, 0] += 1

print("After:")

print(tensor)

def main() raises:

ctx = DeviceContext()

a = ctx.enqueue_create_buffer[dtype](HEIGHT * WIDTH)

a.enqueue_fill(0)

tensor = TileTensor(a, layout)

# Note: since `tensor` is a device tensor we can't print it without the kernel wrapper

ctx.enqueue_function[kernel, kernel](tensor, grid_dim=1, block_dim=1)

ctx.synchronize()

When we run this code with:

pixi run tile_tensor_intro

pixi run -e amd tile_tensor_intro

pixi run -e apple tile_tensor_intro

uv run poe tile_tensor_intro

Before:

0.0 0.0 0.0

0.0 0.0 0.0

After:

1.0 0.0 0.0

0.0 0.0 0.0

Let’s break down what’s happening:

- We create a

2 x 3tensor with row-major layout - Initially, all elements are zero

- Using natural indexing, we modify a single element

- The change is reflected in our output

This simple example demonstrates key TileTensor benefits:

- Clean syntax for tensor creation and access

- Automatic memory layout handling

- Natural multi-dimensional indexing

While this example is straightforward, the same patterns will scale to complex GPU operations in upcoming puzzles. You’ll see how these basic concepts extend to:

- Multi-threaded GPU operations

- Shared memory optimizations

- Complex tiling strategies

- Hardware-accelerated computations

Ready to start your GPU programming journey with TileTensor? Let’s dive into the puzzles!

💡 Tip: Keep this example in mind as we progress - we’ll build upon these fundamental concepts to create increasingly sophisticated GPU programs.

TileTensor Version

Overview

Implement a kernel that adds 10 to each position of 2D TileTensor a and

stores it in 2D TileTensor output.

Note: You have more threads than positions.

Key concepts

In this puzzle, you’ll learn about:

- Using

TileTensorfor 2D array access - Direct 2D indexing with

tensor[i, j] - Handling bounds checking with

TileTensor

The key insight is that TileTensor provides a natural 2D indexing interface,

abstracting away the underlying memory layout while still requiring bounds

checking.

- 2D access: Natural \((i,j)\) indexing with

TileTensor - Memory abstraction: No manual row-major calculation needed

- Guard condition: Still need bounds checking in both dimensions

- Thread bounds: More threads \((3 \times 3)\) than tensor elements \((2 \times 2)\)

Code to complete

comptime SIZE = 2

comptime BLOCKS_PER_GRID = 1

comptime THREADS_PER_BLOCK = (3, 3)

comptime dtype = DType.float32

comptime layout = row_major[SIZE, SIZE]()

comptime LayoutType = type_of(layout)

def add_10_2d(

output: TileTensor[mut=True, dtype, LayoutType, MutAnyOrigin],

a: TileTensor[mut=True, dtype, LayoutType, MutAnyOrigin],

size: Int,

):

var row = thread_idx.y

var col = thread_idx.x

# FILL ME IN (roughly 2 lines)

View full file: problems/p04/p04_tile_tensor.mojo

Tips

- Get 2D indices:

row = thread_idx.y,col = thread_idx.x - Add guard:

if row < size and col < size - Inside guard add 10 to

a[row, col]

Running the code

To test your solution, run the following command in your terminal:

pixi run p04_tile_tensor

pixi run -e amd p04_tile_tensor

pixi run -e apple p04_tile_tensor

uv run poe p04_tile_tensor

Your output will look like this if the puzzle isn’t solved yet:

out: HostBuffer([0.0, 0.0, 0.0, 0.0])

expected: HostBuffer([10.0, 11.0, 12.0, 13.0])

Solution

def add_10_2d(

output: TileTensor[mut=True, dtype, LayoutType, MutAnyOrigin],

a: TileTensor[mut=True, dtype, LayoutType, MutAnyOrigin],

size: Int,

):

var row = thread_idx.y

var col = thread_idx.x

if col < size and row < size:

output[row, col] = a[row, col] + 10.0

This solution:

- Gets 2D thread indices with

row = thread_idx.y,col = thread_idx.x - Guards against out-of-bounds with

if row < size and col < size - Uses

TileTensor’s 2D indexing:output[row, col] = a[row, col] + 10.0

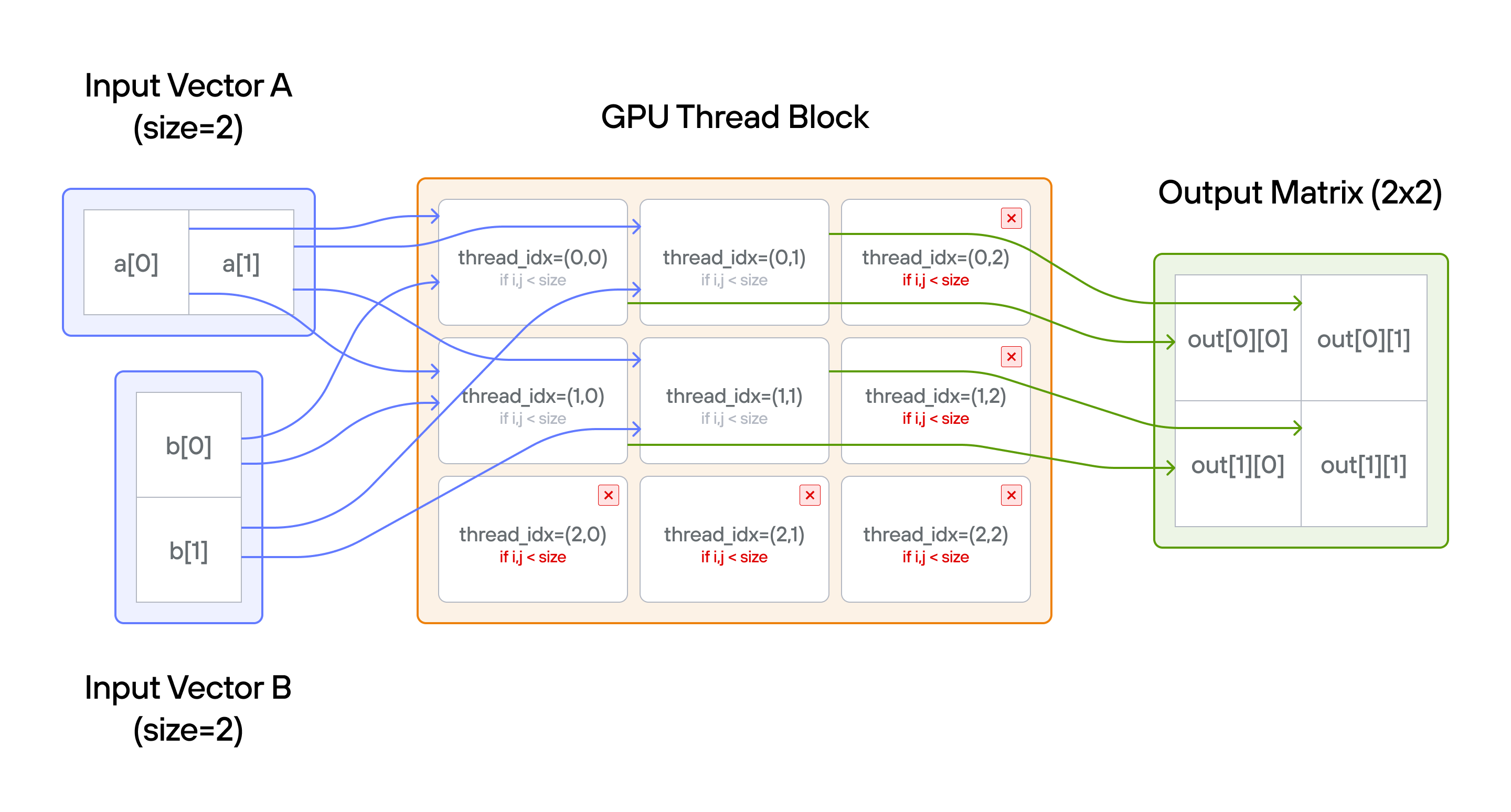

Puzzle 5: Broadcast

Overview

Implement a kernel that broadcast adds 1D TileTensor a and 1D TileTensor b

and stores it in 2D TileTensor output.

Broadcasting in parallel programming refers to the operation where lower-dimensional arrays are automatically expanded to match the shape of higher-dimensional arrays during element-wise operations. Instead of physically replicating data in memory, values are logically repeated across the additional dimensions. For example, adding a 1D vector to each row (or column) of a 2D matrix applies the same vector elements repeatedly without creating multiple copies.

Note: You have more threads than positions.

Key concepts

In this puzzle, you’ll learn about:

- Broadcasting 1D vectors across different dimensions with

TileTensor - Using 2D thread indices to map GPU threads to a 2D output matrix

- Working with different tensor shapes for mixed-dimension operations

- Handling boundary conditions in broadcast patterns

The key insight is that TileTensor allows natural broadcasting through

different tensor shapes: \((1, n)\) and \((n, 1)\) to \((n,n)\), while

still requiring bounds checking.

- Tensor shapes: Input vectors have shapes \((1, n)\) and \((n, 1)\)

- Broadcasting: Each element of

acombines with each element ofb; output expands both dimensions to \((n,n)\) - Access patterns:

a[0, col]broadcasts horizontally across rows;b[row, 0]broadcasts vertically across columns - Guard condition: Still need bounds checking for output size

- Thread bounds: More threads \((3 \times 3)\) than tensor elements \((2 \times 2)\)

Code to complete

comptime SIZE = 2

comptime BLOCKS_PER_GRID = 1

comptime THREADS_PER_BLOCK = (3, 3)

comptime dtype = DType.float32

comptime out_layout = row_major[SIZE, SIZE]()

comptime a_layout = row_major[1, SIZE]()

comptime b_layout = row_major[SIZE, 1]()

comptime OutLayout = type_of(out_layout)

comptime ALayout = type_of(a_layout)

comptime BLayout = type_of(b_layout)

def broadcast_add(

output: TileTensor[mut=True, dtype, OutLayout, MutAnyOrigin],

a: TileTensor[mut=False, dtype, ALayout, ImmutAnyOrigin],

b: TileTensor[mut=False, dtype, BLayout, ImmutAnyOrigin],

size: Int,

):

var row = thread_idx.y

var col = thread_idx.x

# FILL ME IN (roughly 2 lines)

View full file: problems/p05/p05.mojo

Tips

- Get 2D indices:

row = thread_idx.y,col = thread_idx.x - Add guard:

if row < size and col < size - Inside guard: think about how to broadcast values of

aandbas TileTensors

Running the code

To test your solution, run the following command in your terminal:

pixi run p05

pixi run -e amd p05

pixi run -e apple p05

uv run poe p05

Your output will look like this if the puzzle isn’t solved yet:

out: HostBuffer([0.0, 0.0, 0.0, 0.0])

expected: HostBuffer([1.0, 2.0, 11.0, 12.0])

Solution

def broadcast_add(

output: TileTensor[mut=True, dtype, OutLayout, MutAnyOrigin],

a: TileTensor[mut=False, dtype, ALayout, ImmutAnyOrigin],

b: TileTensor[mut=False, dtype, BLayout, ImmutAnyOrigin],

size: Int,

):

var row = thread_idx.y

var col = thread_idx.x

if row < size and col < size:

output[row, col] = a[0, col] + b[row, 0]

This solution demonstrates key concepts of TileTensor broadcasting and GPU thread mapping:

-

Thread to matrix mapping

- Uses

thread_idx.yfor row access andthread_idx.xfor column access - Natural 2D indexing matches the output matrix structure

- Excess threads (3×3 grid) are handled by bounds checking

- Uses

-

Broadcasting mechanics

- Input

ahas shape(1,n):a[0,col]broadcasts across rows - Input

bhas shape(n,1):b[row,0]broadcasts across columns - Output has shape

(n,n): Each element is sum of corresponding broadcasts

[ a0 a1 ] + [ b0 ] = [ a0+b0 a1+b0 ] [ b1 ] [ a0+b1 a1+b1 ] - Input

-

Bounds Checking

- Guard condition

row < size and col < sizeprevents out-of-bounds access - Handles both matrix bounds and excess threads efficiently

- No need for separate checks for

aandbdue to broadcasting

- Guard condition

This pattern forms the foundation for more complex tensor operations we’ll explore in later puzzles.

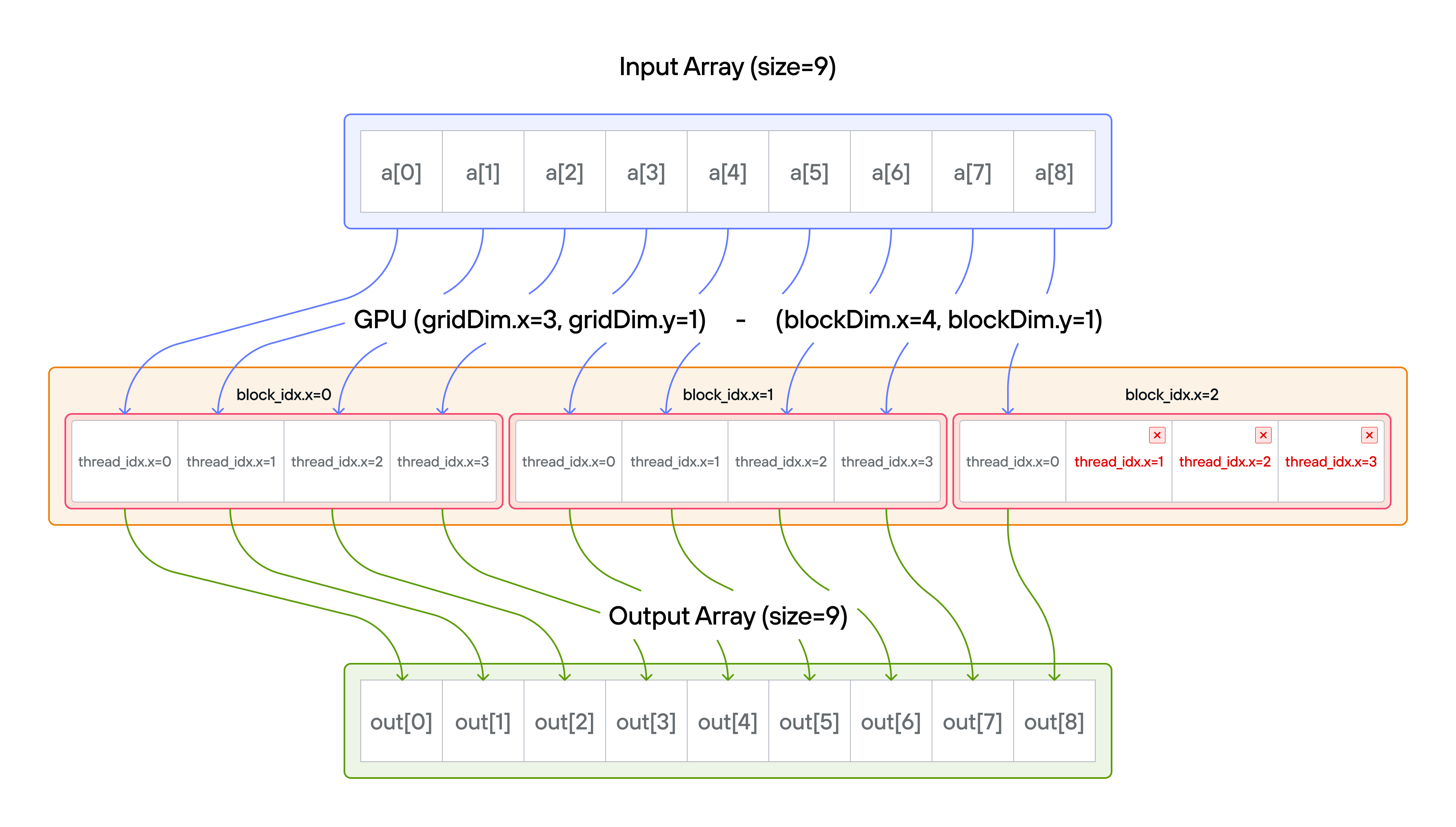

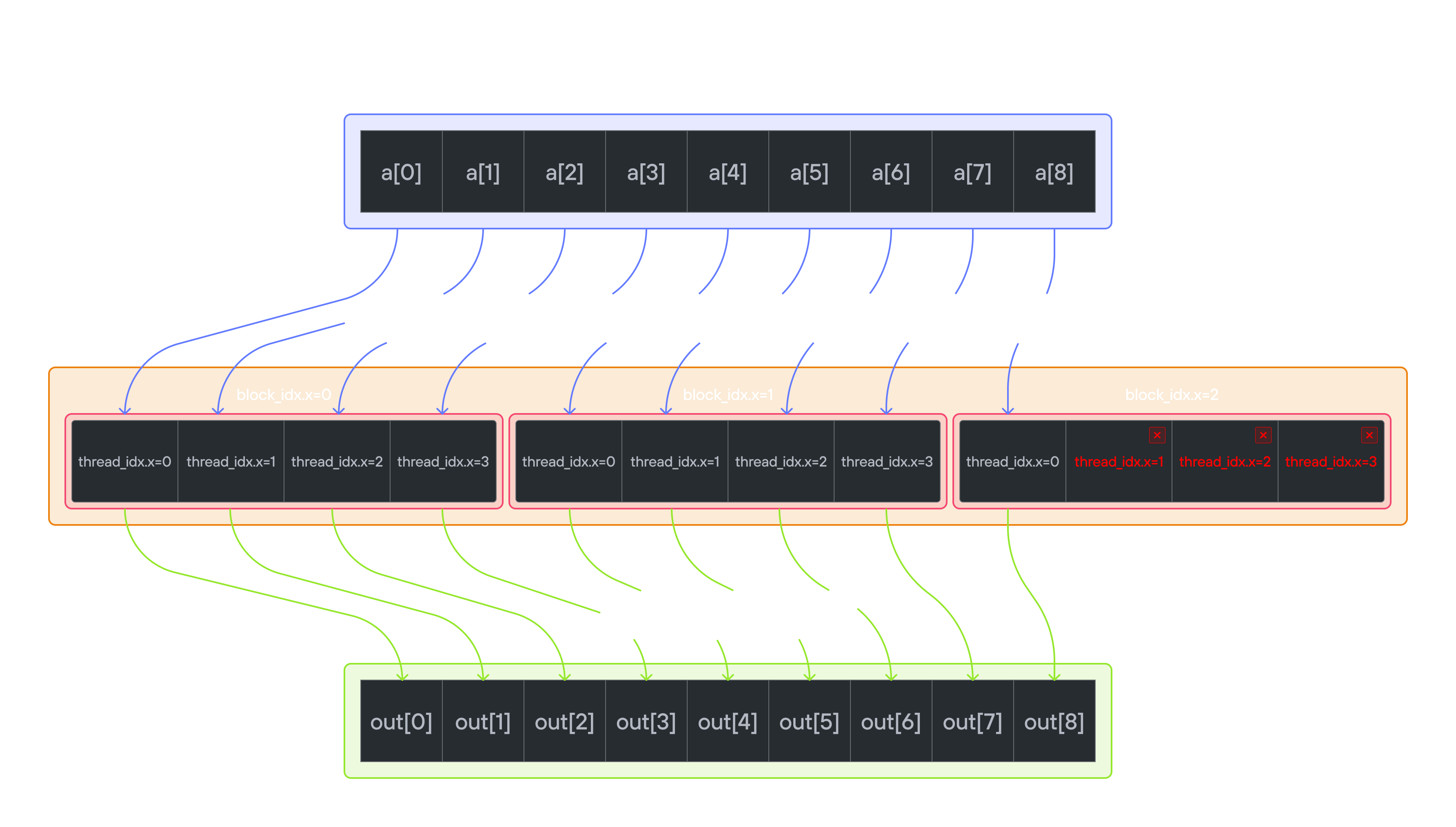

Puzzle 6: Blocks

Overview

Implement a kernel that adds 10 to each position of vector a and stores it in

output.

A thread block (or just block) is a group of threads that execute

together on a single GPU multiprocessor. All threads in a block share the same

shared memory and can synchronize with each other. When data is larger than one

block can handle, the GPU schedules multiple blocks — each block independently

processes its portion of the data. The global position of a thread is computed

from both its position within the block (thread_idx.x) and which block it

belongs to (block_idx.x):

global_i = block_dim.x * block_idx.x + thread_idx.x.

Note: You have fewer threads per block than the size of a.

Key concepts

This puzzle covers:

- Processing data larger than thread block size

- Coordinating multiple blocks of threads

- Computing global thread positions

The key insight is understanding how blocks of threads work together to process data that’s larger than a single block’s capacity, while maintaining correct element-to-thread mapping.

Code to complete

comptime SIZE = 9

comptime BLOCKS_PER_GRID = (3, 1)

comptime THREADS_PER_BLOCK = (4, 1)

comptime dtype = DType.float32

def add_10_blocks(

output: UnsafePointer[Scalar[dtype], MutAnyOrigin],

a: UnsafePointer[Scalar[dtype], MutAnyOrigin],

size: Int,

):

var i = block_dim.x * block_idx.x + thread_idx.x

# FILL ME IN (roughly 2 lines)

View full file: problems/p06/p06.mojo

Note: The

TileTensorvariant of this puzzle is very similar so we leave it to the reader.

Tips

- Calculate global index:

i = block_dim.x * block_idx.x + thread_idx.x - Add guard:

if i < size - Inside guard:

output[i] = a[i] + 10.0

Running the code

To test your solution, run the following command in your terminal:

pixi run p06

pixi run -e amd p06

pixi run -e apple p06

uv run poe p06

Your output will look like this if the puzzle isn’t solved yet:

out: HostBuffer([0.0, 0.0, 0.0, 0.0, 0.0, 0.0, 0.0, 0.0, 0.0])

expected: HostBuffer([10.0, 11.0, 12.0, 13.0, 14.0, 15.0, 16.0, 17.0, 18.0])

Solution

def add_10_blocks(

output: UnsafePointer[Scalar[dtype], MutAnyOrigin],

a: UnsafePointer[Scalar[dtype], MutAnyOrigin],

size: Int,

):

var i = block_dim.x * block_idx.x + thread_idx.x

if i < size:

output[i] = a[i] + 10.0

This solution covers key concepts of block-based GPU processing:

-

Global thread indexing

-

Combines block and thread indices:

block_dim.x * block_idx.x + thread_idx.x -

Maps each thread to a unique global position

-

Example for 3 threads per block:

Block 0: [0 1 2] Block 1: [3 4 5] Block 2: [6 7 8]

-

-

Block coordination

-

Each block processes a contiguous chunk of data

-

Block size (3) < Data size (9) requires multiple blocks

-

Automatic work distribution across blocks:

Data: [0 1 2 3 4 5 6 7 8] Block 0: [0 1 2] Block 1: [3 4 5] Block 2: [6 7 8]

-

-

Bounds checking

- Guard condition

i < sizehandles edge cases - Prevents out-of-bounds access when size isn’t perfectly divisible by block size

- Essential for handling partial blocks at the end of data

- Guard condition

-

Memory access pattern

- Coalesced memory access: threads in a block access contiguous memory

- Each thread processes one element:

output[i] = a[i] + 10.0 - Block-level parallelism provides efficient memory bandwidth utilization

This pattern forms the foundation for processing large datasets that exceed the size of a single thread block.

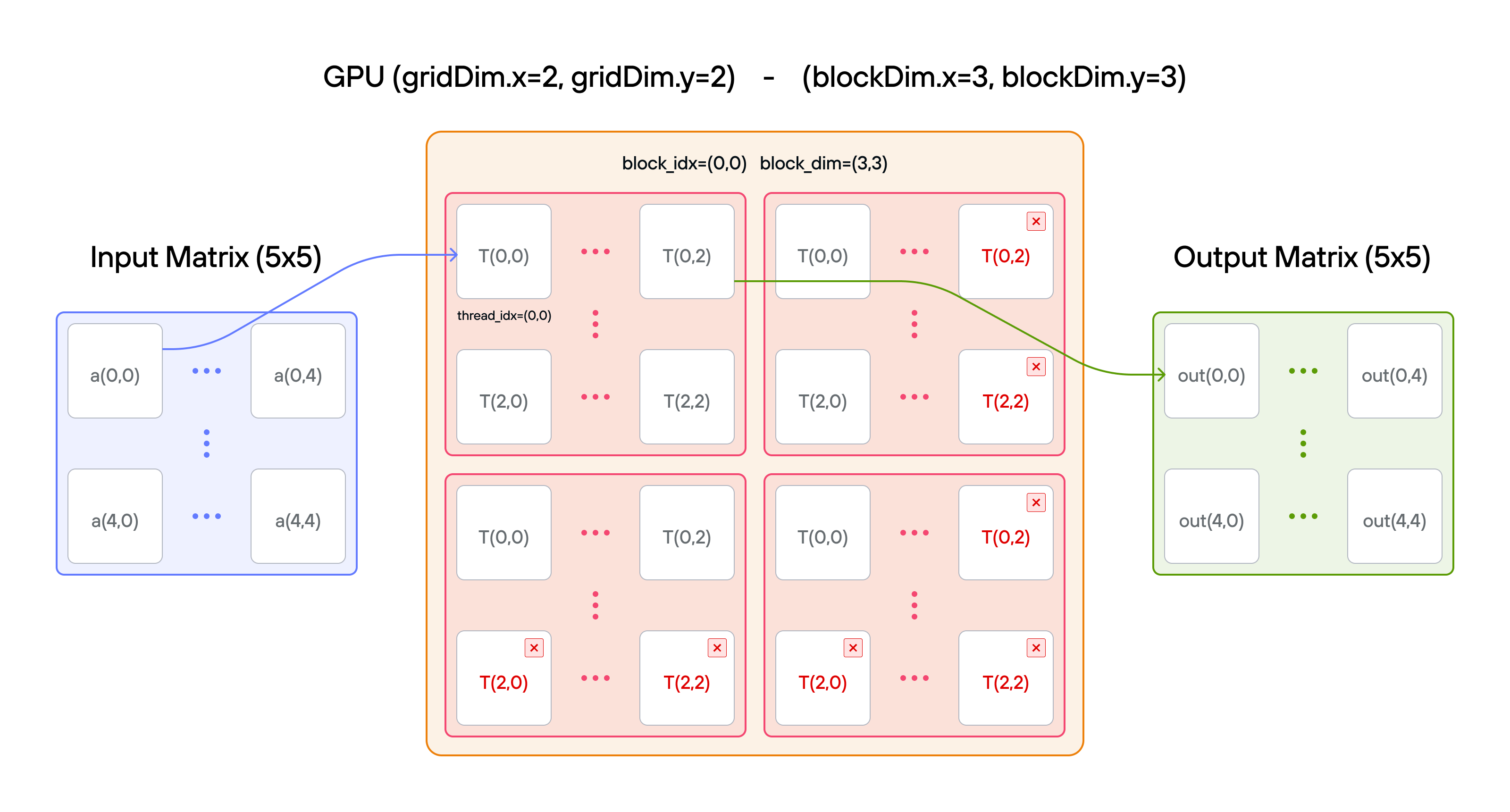

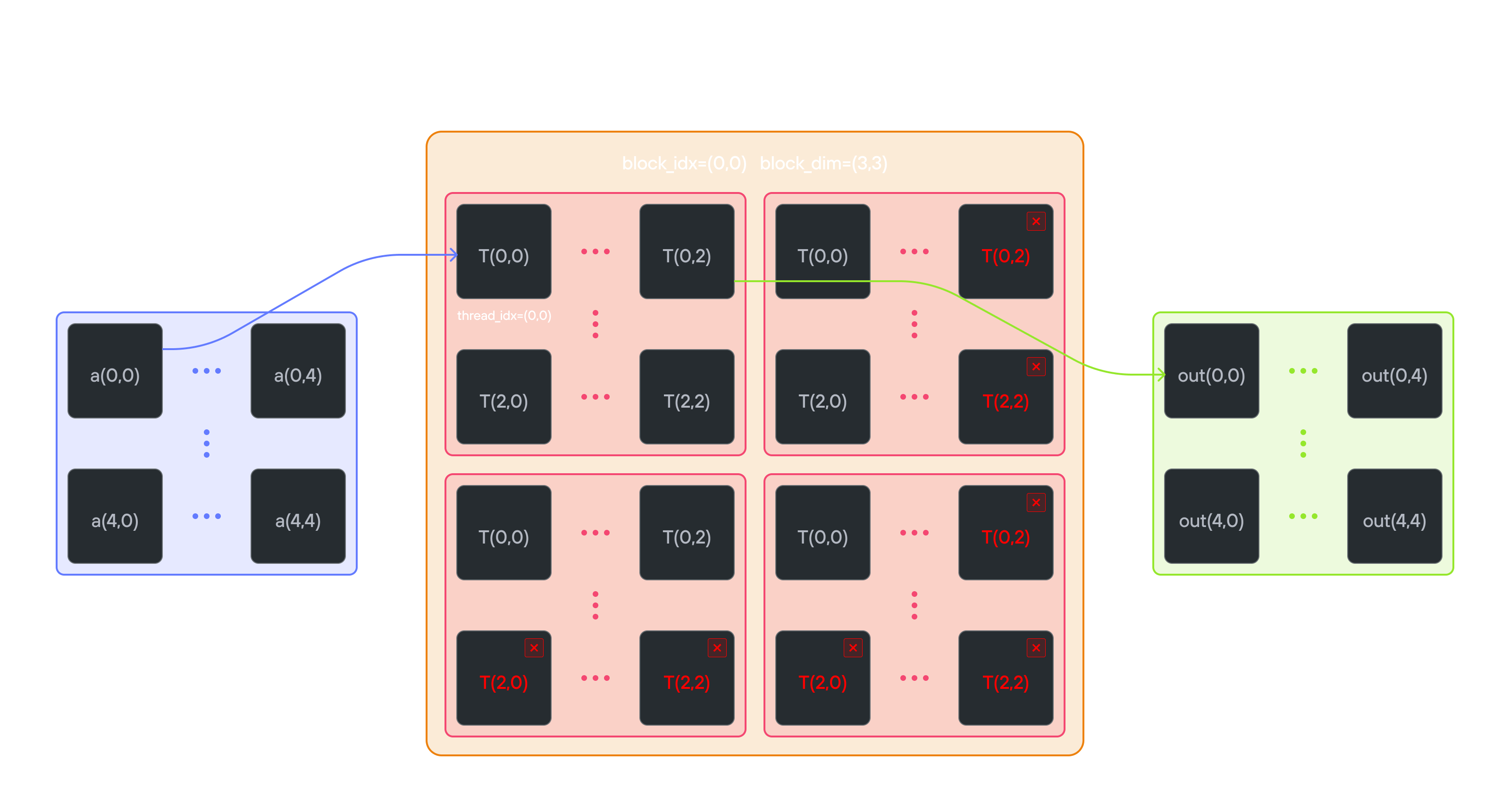

Puzzle 7: 2D Blocks

Overview

Implement a kernel that adds 10 to each position of 2D TileTensor a and stores

it in 2D TileTensor output.

Note:

You have fewer threads per block than the size of a in both directions.

Key concepts

In this puzzle, you’ll learn about:

- Using

TileTensorwith multiple blocks - Handling large matrices with 2D block organization

- Combining block indexing with

TileTensoraccess

The key insight is that TileTensor simplifies 2D indexing while still

requiring proper block coordination for large matrices.

🔑 2D thread indexing convention

We extend the block-based indexing from puzzle 4 to 2D:

Global position calculation: row = block_dim.y * block_idx.y + thread_idx.y col = block_dim.x * block_idx.x + thread_idx.xFor example, with 2×2 blocks in a 4×4 grid:

Block (0,0): Block (1,0): [0,0 0,1] [0,2 0,3] [1,0 1,1] [1,2 1,3] Block (0,1): Block (1,1): [2,0 2,1] [2,2 2,3] [3,0 3,1] [3,2 3,3]Each position shows (row, col) for that thread’s global index. The block dimensions and indices work together to ensure:

- Continuous coverage of the 2D space

- No overlap between blocks

- Efficient memory access patterns

Configuration

- Matrix size: \(5 \times 5\) elements

- Layout handling:

TileTensormanages row-major organization - Block coordination: Multiple blocks cover the full matrix

- 2D indexing: Natural \((i,j)\) access with bounds checking

- Total threads: \(36\) for \(25\) elements

- Thread mapping: Each thread processes one matrix element

Code to complete

comptime SIZE = 5

comptime BLOCKS_PER_GRID = (2, 2)

comptime THREADS_PER_BLOCK = (3, 3)

comptime dtype = DType.float32

comptime out_layout = row_major[SIZE, SIZE]()

comptime a_layout = row_major[SIZE, SIZE]()

comptime OutLayout = type_of(out_layout)

comptime ALayout = type_of(a_layout)

def add_10_blocks_2d(

output: TileTensor[mut=True, dtype, OutLayout, MutAnyOrigin],

a: TileTensor[mut=False, dtype, ALayout, ImmutAnyOrigin],

size: Int,

):

var row = block_dim.y * block_idx.y + thread_idx.y

var col = block_dim.x * block_idx.x + thread_idx.x

# FILL ME IN (roughly 2 lines)

View full file: problems/p07/p07.mojo

Tips

- Calculate global indices:

row = block_dim.y * block_idx.y + thread_idx.y,col = block_dim.x * block_idx.x + thread_idx.x - Add guard:

if row < size and col < size - Inside guard: think about how to add 10 to 2D TileTensor

Running the code

To test your solution, run the following command in your terminal:

pixi run p07

pixi run -e amd p07

pixi run -e apple p07

uv run poe p07

Your output will look like this if the puzzle isn’t solved yet:

out: HostBuffer([0.0, 0.0, 0.0, ... , 0.0])

expected: HostBuffer([10.0, 11.0, 12.0, ... , 34.0])

Solution

def add_10_blocks_2d(

output: TileTensor[mut=True, dtype, OutLayout, MutAnyOrigin],

a: TileTensor[mut=False, dtype, ALayout, ImmutAnyOrigin],

size: Int,

):

var row = block_dim.y * block_idx.y + thread_idx.y

var col = block_dim.x * block_idx.x + thread_idx.x

if row < size and col < size:

output[row, col] = a[row, col] + 10.0

This solution demonstrates how TileTensor simplifies 2D block-based processing:

-

2D thread indexing

-

Global row:

block_dim.y * block_idx.y + thread_idx.y -

Global col:

block_dim.x * block_idx.x + thread_idx.x -

Maps thread grid to tensor elements:

5×5 tensor with 3×3 blocks: Block (0,0) Block (1,0) [(0,0) (0,1) (0,2)] [(0,3) (0,4) * ] [(1,0) (1,1) (1,2)] [(1,3) (1,4) * ] [(2,0) (2,1) (2,2)] [(2,3) (2,4) * ] Block (0,1) Block (1,1) [(3,0) (3,1) (3,2)] [(3,3) (3,4) * ] [(4,0) (4,1) (4,2)] [(4,3) (4,4) * ] [ * * * ] [ * * * ](* = thread exists but outside tensor bounds)

-

-

TileTensor benefits

-

Natural 2D indexing:

tensor[row, col]instead of manual offset calculation -

Automatic memory layout optimization

-

Example access pattern:

Raw memory: TileTensor: row * size + col tensor[row, col] (2,1) -> 11 (2,1) -> same element

-

-

Bounds checking

- Guard

row < size and col < sizehandles:- Excess threads in partial blocks

- Edge cases at tensor boundaries

- Automatic memory layout handling by TileTensor

- 36 threads (2×2 blocks of 3×3) for 25 elements

- Guard

-

Block coordination

- Each 3×3 block processes part of 5×5 tensor

- TileTensor handles:

- Memory layout optimization

- Efficient access patterns

- Block boundary coordination

- Cache-friendly data access

This pattern shows how TileTensor simplifies 2D block processing while maintaining optimal memory access patterns and thread coordination.

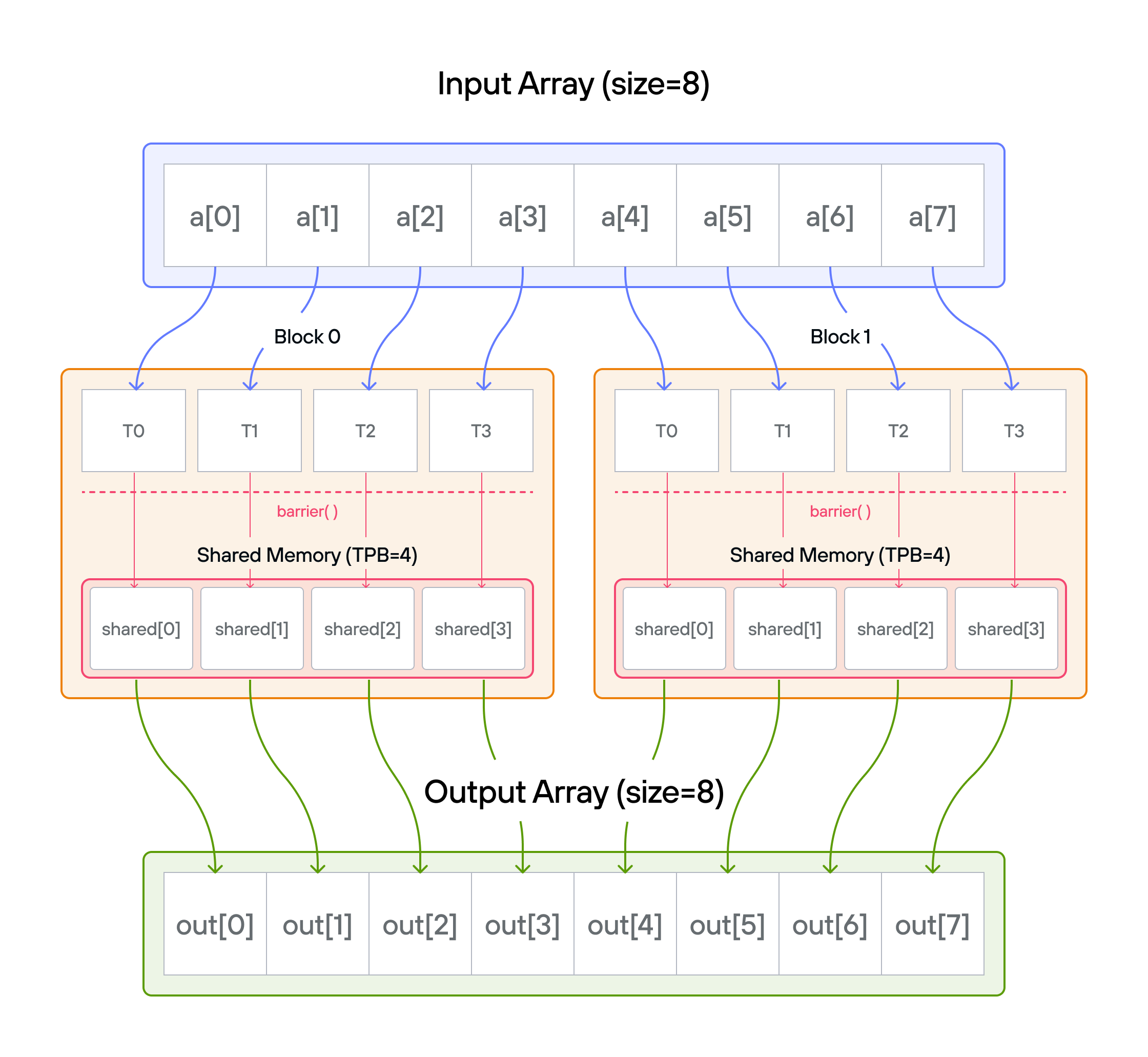

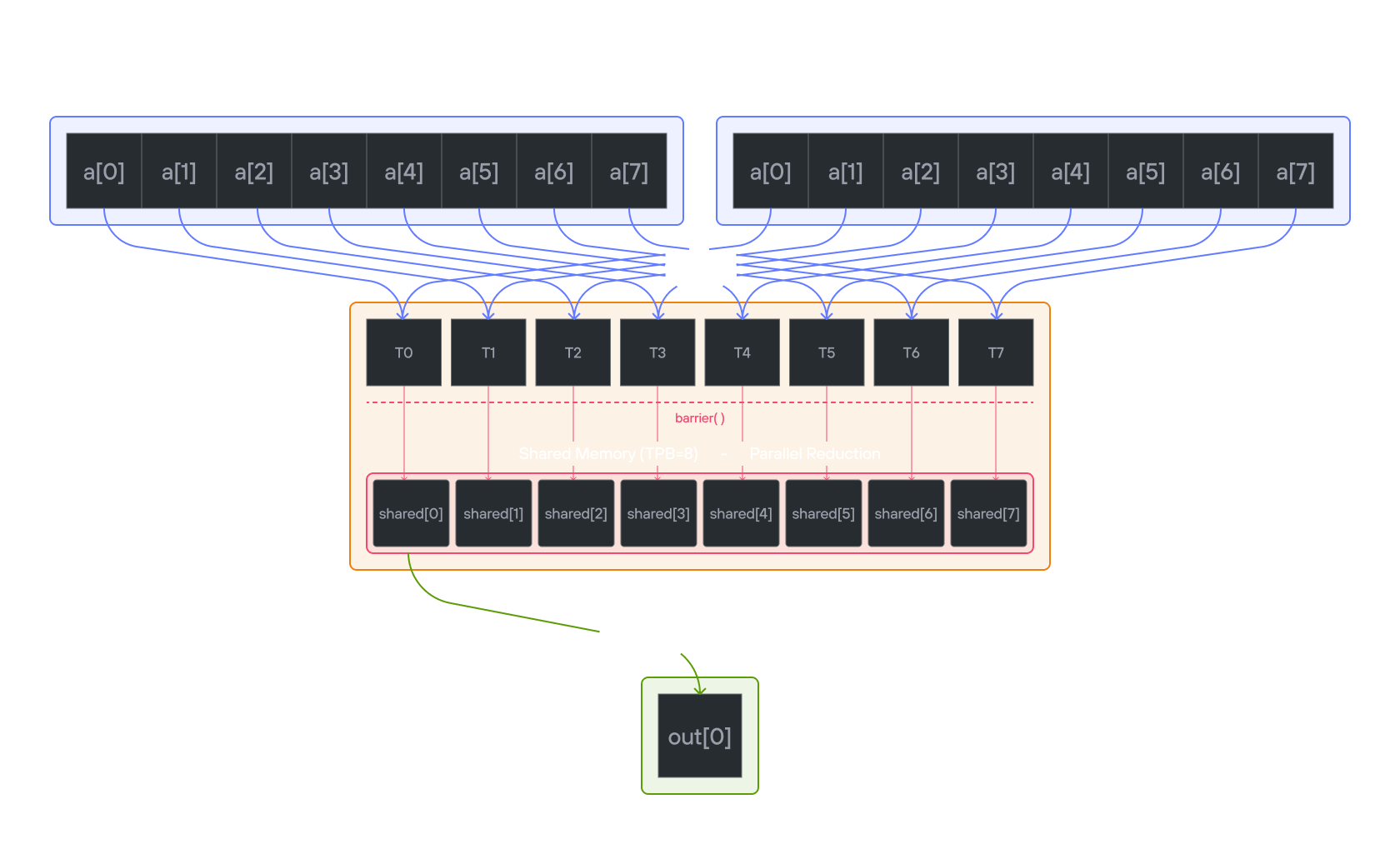

Puzzle 8: Shared Memory

Overview

Implement a kernel that adds 10 to each position of a 1D TileTensor a and

stores it in 1D TileTensor output.

Shared memory is fast, on-chip storage that is visible to all threads within

the same block. Unlike global memory (which all blocks can access but is slow),

shared memory has latency similar to a CPU register cache. Each block gets its

own private shared memory region — threads in one block cannot see the shared

memory of another block. Because threads can read and write to the same shared

memory locations, coordination via barrier() is required to prevent one thread

from reading a value before another thread has finished writing it.

Note: You have fewer threads per block than the size of a.

Key concepts

In this puzzle, you’ll learn about:

- Using TileTensor’s shared memory features with address_space

- Thread synchronization with shared memory

- Block-local data management with TileTensor

The key insight is how TileTensor simplifies shared memory management while maintaining the performance benefits of block-local storage.

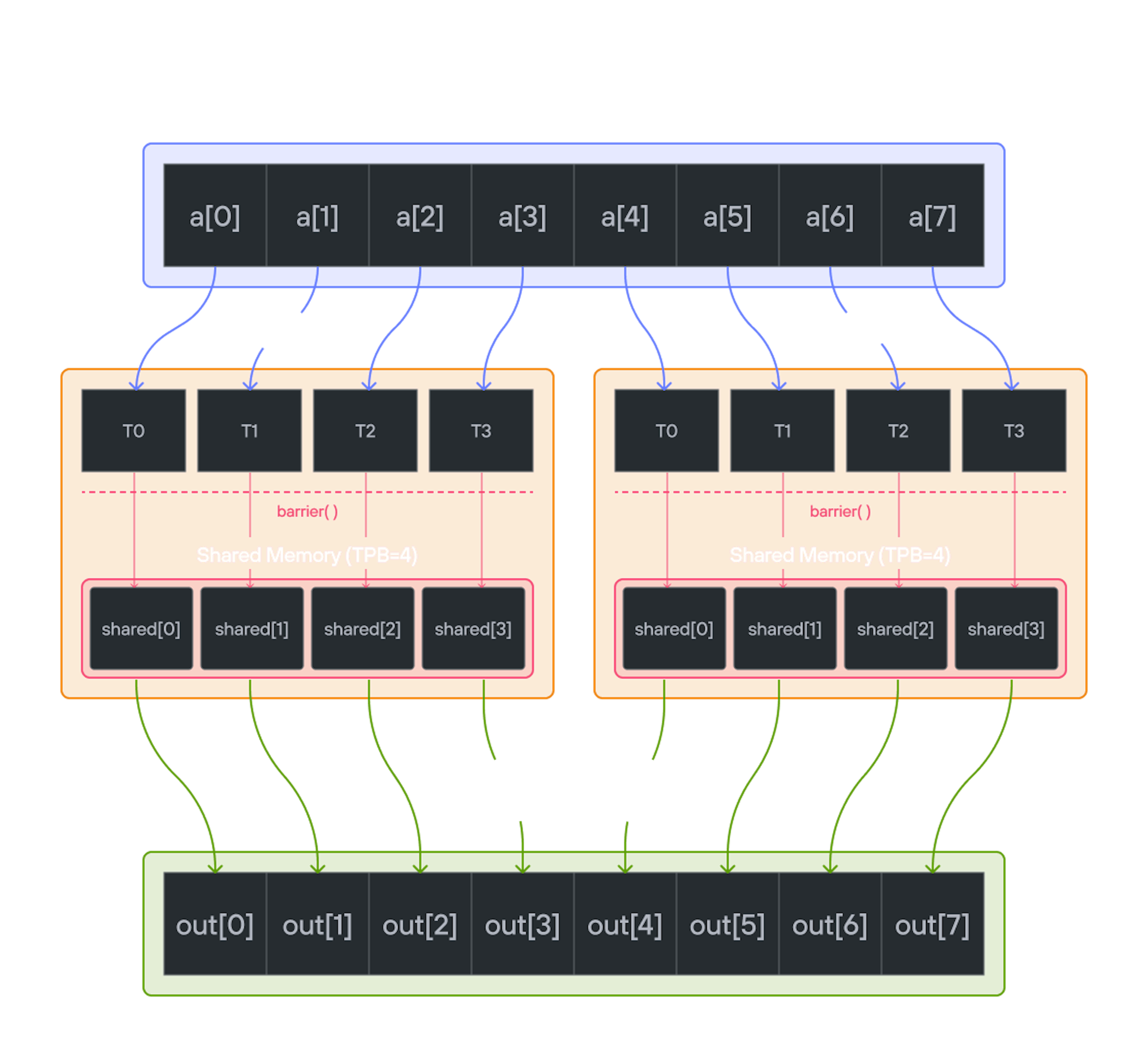

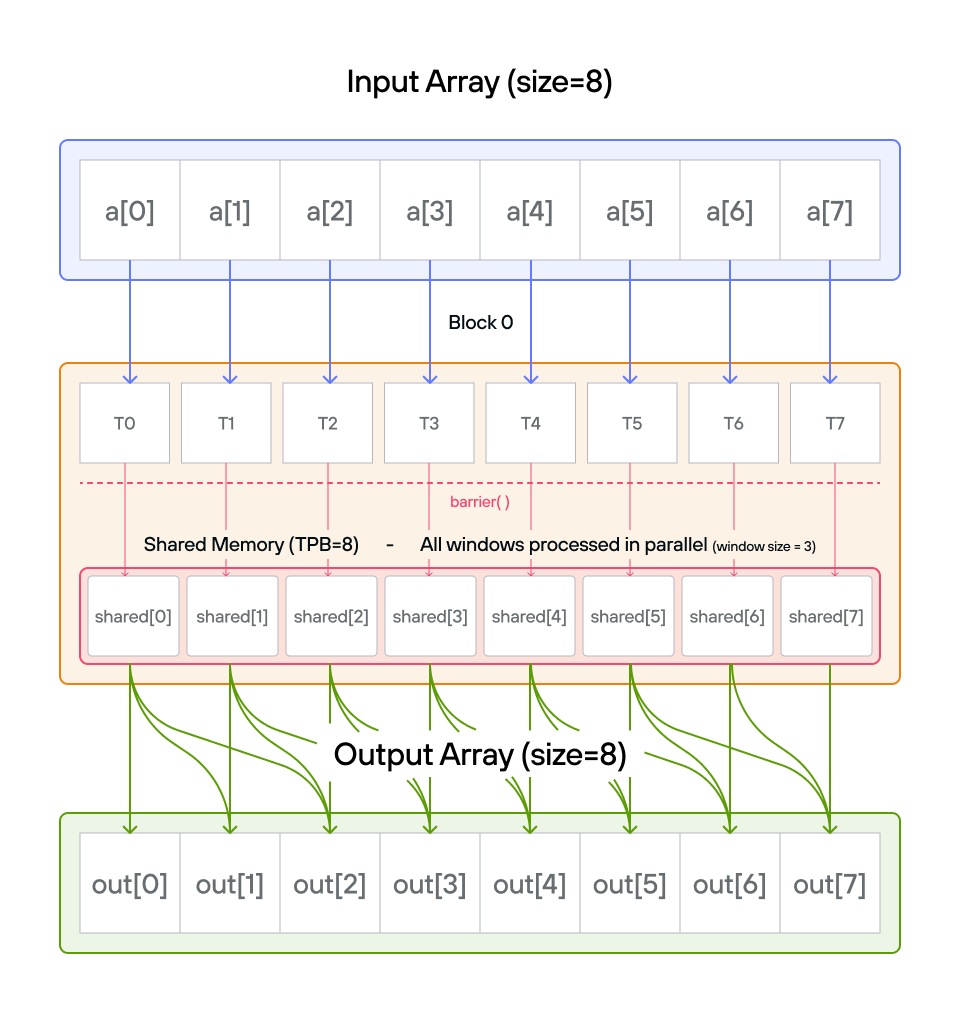

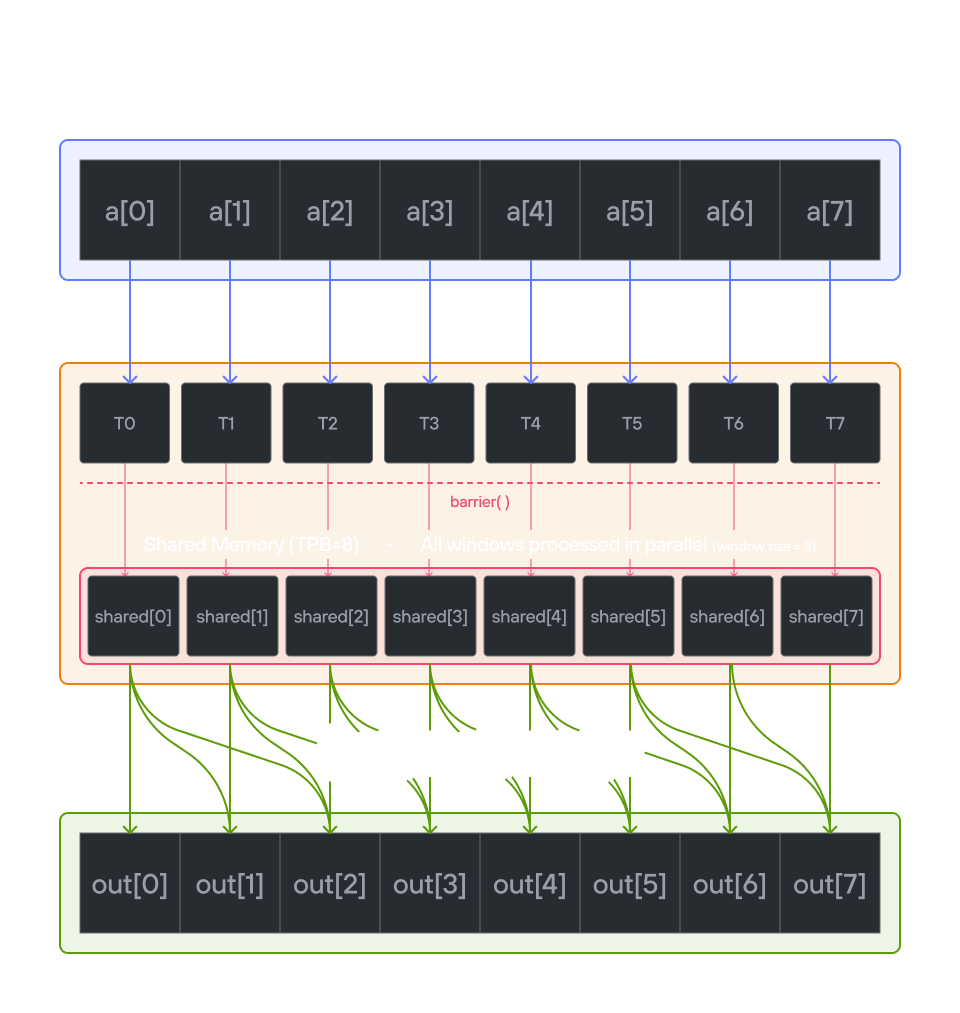

Configuration

- Array size:

SIZE = 8elements - Threads per block:

TPB = 4 - Number of blocks: 2

- Shared memory:

TPBelements per block

Warning: Each block can only have a constant amount of shared memory that threads in that block can read and write to. This needs to be a literal python constant, not a variable. After writing to shared memory you need to call barrier to ensure that threads do not cross.

Educational Note: In this specific puzzle, the barrier() isn’t strictly

necessary since each thread only accesses its own shared memory location.

However, it’s included to teach proper shared memory synchronization patterns

for more complex scenarios where threads need to coordinate access to shared

data.

Code to complete

comptime TPB = 4

comptime SIZE = 8

comptime BLOCKS_PER_GRID = (2, 1)

comptime THREADS_PER_BLOCK = (TPB, 1)

comptime dtype = DType.float32

comptime layout = row_major[SIZE]()

comptime LayoutType = type_of(layout)

def add_10_shared(

output: TileTensor[mut=True, dtype, LayoutType, MutAnyOrigin],

a: TileTensor[mut=False, dtype, LayoutType, ImmutAnyOrigin],

size: Int,

):

# Allocate shared memory using stack_allocation

var shared = stack_allocation[

dtype=dtype, address_space=AddressSpace.SHARED

](row_major[TPB]())

var global_i = block_dim.x * block_idx.x + thread_idx.x

var local_i = thread_idx.x

if global_i < size:

shared[local_i] = a[global_i]

barrier()

# FILL ME IN (roughly 2 lines)

View full file: problems/p08/p08.mojo

Tips

- Create shared memory with TileTensor using address_space parameter

- Load data with natural indexing:

shared[local_i] = a[global_i] - Synchronize with

barrier()(educational - not strictly needed here) - Process data using shared memory indices

- Guard against out-of-bounds access

Running the code

To test your solution, run the following command in your terminal:

pixi run p08

pixi run -e amd p08

pixi run -e apple p08

uv run poe p08

Your output will look like this if the puzzle isn’t solved yet:

out: HostBuffer([0.0, 0.0, 0.0, 0.0, 0.0, 0.0, 0.0, 0.0])

expected: HostBuffer([11.0, 11.0, 11.0, 11.0, 11.0, 11.0, 11.0, 11.0])

Solution

def add_10_shared_tile_tensor(

output: TileTensor[mut=True, dtype, LayoutType, MutAnyOrigin],

a: TileTensor[mut=False, dtype, LayoutType, ImmutAnyOrigin],

size: Int,

):

# Allocate shared memory using stack_allocation

var shared = stack_allocation[

dtype=dtype, address_space=AddressSpace.SHARED

](row_major[TPB]())

var global_i = block_dim.x * block_idx.x + thread_idx.x

var local_i = thread_idx.x

if global_i < size:

shared[local_i] = a[global_i]

# Note: barrier is not strictly needed here since each thread only accesses

# its own shared memory location. However, it's included to teach proper

# shared memory synchronization patterns for more complex scenarios where

# threads need to coordinate access to shared data.

barrier()

if global_i < size:

output[global_i] = shared[local_i] + 10

This solution demonstrates how TileTensor simplifies shared memory usage while maintaining performance:

-

Memory hierarchy with TileTensor

-

Global tensors:

aandoutput(slow, visible to all blocks) -

Shared tensor:

shared(fast, thread-block local) -

Example for 8 elements with 4 threads per block:

Global tensor a: [1 1 1 1 | 1 1 1 1] # Input: all ones Block (0): Block (1): shared[0..3] shared[0..3] [1 1 1 1] [1 1 1 1]

-

-

Thread coordination

-

Load phase with natural indexing:

Thread 0: shared[0] = a[0]=1 Thread 2: shared[2] = a[2]=1 Thread 1: shared[1] = a[1]=1 Thread 3: shared[3] = a[3]=1 barrier() ↓ ↓ ↓ ↓ # Wait for all loads -

Process phase: Each thread adds 10 to its shared tensor value

-

Result:

output[global_i] = shared[local_i] + 10 = 11

-

Note: In this specific case, the barrier() isn’t strictly necessary since

each thread only writes to and reads from its own shared memory location

(shared[local_i]). However, it’s included for educational purposes to

demonstrate proper shared memory synchronization patterns that are essential

when threads need to access each other’s data.

-

TileTensor benefits

-

Shared memory allocation:

# Clean TileTensor API with address_space shared = stack_allocation[dtype=dtype, address_space=AddressSpace.SHARED](row_major[TPB]()) -

Natural indexing for both global and shared:

Block 0 output: [11 11 11 11] Block 1 output: [11 11 11 11] -

Built-in layout management and type safety

-

-

Memory access pattern

- Load: Global tensor → Shared tensor (optimized)

- Sync: Same

barrier()requirement as raw version - Process: Add 10 to shared values

- Store: Write 11s back to global tensor

This pattern shows how TileTensor maintains the performance benefits of shared memory while providing a more ergonomic API and built-in features.

Puzzle 9: GPU Debugging Workflow

⚠️ This puzzle works on compatible NVIDIA GPU only. We are working to enable tooling support for other GPU vendors.

When GPU programs fail

You’ve written GPU kernels, worked with shared memory, and coordinated thousands of parallel threads. Your code compiles. You run it expecting correct results, and then:

- CRASH

- Wrong results

- Infinite hang

This is GPU programming reality: debugging parallel code running on thousands of threads simultaneously. This is where theory meets practice, where algorithmic knowledge meets investigative skills.

Why GPU debugging is challenging

Unlike traditional CPU debugging where you follow a single thread through sequential execution, GPU debugging requires you to:

- Think in parallel: Thousands of threads executing simultaneously, each potentially doing something different

- Navigate multiple memory spaces: Global memory, shared memory, registers, constant memory

- Handle coordination failures: Race conditions, barrier deadlocks, memory access violations

- Debug optimized code: JIT compilation, variable optimization, limited symbol information

- Use specialized tools: CUDA-GDB for kernel inspection, thread navigation, parallel state analysis

GPU debugging skills provide deep understanding of parallel computing fundamentals.

What you’ll learn in this puzzle

This puzzle teaches you to debug GPU code systematically. You’ll learn the approaches, tools, and techniques that GPU developers use daily to solve complex parallel programming challenges.

Essential skills you’ll develop

- Professional debugging workflow - The systematic approach professionals use

- Tool proficiency - LLDB for host code, CUDA-GDB for GPU kernels

- Pattern recognition - Common GPU bug types and symptoms

- Investigation techniques - Finding root causes when variables are optimized out

- Thread coordination debugging - Advanced GPU debugging skills

Real-world debugging scenarios

You’ll tackle the three most common GPU programming failures:

- Memory crashes - Null pointers, illegal memory access, segmentation faults

- Logic bugs - Correct execution with wrong results, algorithmic errors

- Coordination deadlocks - Barrier synchronization failures, infinite hangs

Each scenario teaches different investigation techniques and builds debugging intuition.

Your debugging journey

This puzzle takes you through a carefully designed progression from basic debugging concepts to advanced parallel coordination failures:

📚 Step 1: Mojo GPU Debugging Essentials

Foundation building - Learn the tools and workflow

- Set up your debugging environment with

pixiand CUDA-GDB - Learn the four debugging approaches: JIT vs binary, CPU vs GPU

- Learn essential CUDA-GDB commands for GPU kernel inspection

- Practice with hands-on examples using familiar code from previous puzzles

- Understand when to use each debugging approach

Key outcome: Professional debugging workflow and tool proficiency

🧐 Step 2: Detective Work: First Case

Memory crash investigation - Debug a GPU program that crashes

- Investigate

CUDA_ERROR_ILLEGAL_ADDRESScrashes - Learn systematic pointer inspection techniques

- Learn null pointer detection and validation

- Practice professional crash analysis workflow

- Understand GPU memory access failures

Key outcome: Ability to debug GPU memory crashes and pointer issues

🔍 Step 3: Detective Work: Second Case

Logic bug investigation - Debug a program with wrong results

- Investigate TileTensor-based algorithmic errors

- Learn execution flow analysis when variables are optimized out

- Learn loop boundary analysis and iteration counting

- Practice pattern recognition in incorrect results

- Debug without direct variable inspection

Key outcome: Ability to debug algorithmic errors and logic bugs in GPU kernels

🕵️ Step 4: Detective Work: Third Case

Barrier deadlock investigation - Debug a program that hangs forever

- Investigate barrier synchronization failures

- Learn multi-thread state analysis across parallel execution

- Learn conditional execution path tracing

- Practice thread coordination debugging

- Understand the most challenging GPU debugging scenario

Key outcome: Advanced thread coordination debugging - the pinnacle of GPU debugging skills

The detective mindset

GPU debugging requires a different mindset than traditional programming. You become a detective investigating a crime scene where:

- The evidence is limited - Variables are optimized out, symbols are mangled

- Multiple suspects exist - Thousands of threads, any could be the culprit

- The timeline is complex - Parallel execution, race conditions, timing dependencies

- The tools are specialized - CUDA-GDB, thread navigation, GPU memory inspection

But like any good detective, you’ll learn to:

- Follow the clues systematically - Error messages, crash patterns, thread states

- Form hypotheses - What could cause this specific behavior?

- Test theories - Use debugging commands to verify or disprove ideas

- Trace back to root causes - From symptoms to the actual source of problems

Prerequisites and expectations

What you need to know:

- GPU programming concepts from Puzzles 1-8 (thread indexing, memory management, barriers)

- Basic command-line comfort (you’ll use terminal-based debugging tools)

- Patience and systematic thinking (GPU debugging requires methodical investigation)

What you’ll gain:

- Professional debugging skills used in GPU development teams

- Deep parallel computing understanding that comes from seeing execution at the thread level

- Problem-solving confidence for the most challenging GPU programming scenarios

- Tool proficiency that will serve you throughout your GPU programming career

Ready to begin?

GPU debugging is where you transition from writing GPU programs to understanding them deeply. Every professional GPU developer has spent countless hours debugging parallel code, learning to think in thousands of simultaneous threads, and developing the patience to investigate complex coordination failures.

This is your opportunity to join that elite group.

Start your debugging journey: Mojo GPU Debugging Essentials

“Debugging is twice as hard as writing the code in the first place. Therefore, if you write the code as cleverly as possible, you are, by definition, not smart enough to debug it.” - Brian Kernighan

In GPU programming, this wisdom is amplified by a factor of thousands - the number of parallel threads you’re debugging simultaneously.

📚 Mojo GPU Debugging Essentials

Welcome to the world of GPU debugging! After learning GPU programming concepts through puzzles 1-8, you’re now ready to learn the most critical skill for any GPU programmer: how to debug when things go wrong.

GPU debugging can seem intimidating at first - you’re dealing with thousands of threads running in parallel, different memory spaces, and hardware-specific behaviors. But with the right tools and workflow, debugging GPU code becomes systematic and manageable.

In this guide, you’ll learn to debug both the CPU host code (where you set up your GPU operations) and the GPU kernel code (where the parallel computation happens). We’ll use real examples, actual debugger output, and step-by-step workflows that you can immediately apply to your own projects.

Note: The following content focuses on command-line debugging for universal IDE compatibility. If you prefer VS Code debugging, refer to the Mojo debugging documentation for VS Code-specific setup and workflows.

Why GPU debugging is different

Before diving into tools, consider what makes GPU debugging unique:

- Traditional CPU debugging: One thread, sequential execution, straightforward memory model

- GPU debugging: Thousands of threads, parallel execution, multiple memory spaces, race conditions

This means you need specialized tools that can:

- Switch between different GPU threads

- Inspect thread-specific variables and memory

- Handle the complexity of parallel execution

- Debug both CPU setup code and GPU kernel code

Your debugging toolkit

Mojo’s GPU debugging capabilities currently is limited to NVIDIA GPUs. The Mojo debugging documentation explains that the Mojo package includes:

- LLDB debugger with Mojo plugin for CPU-side debugging

- CUDA-GDB integration for GPU kernel debugging

- Command-line interface via

mojo debugfor universal IDE compatibility

For GPU-specific debugging, the Mojo GPU debugging guide provides additional technical details.

This architecture provides the best of both worlds: familiar debugging commands with GPU-specific capabilities.

The debugging workflow: From problem to solution

When your GPU program crashes, produces wrong results, or behaves unexpectedly, follow this systematic approach:

- Prepare your code for debugging (disable optimizations, add debug symbols)

- Choose the right debugger (CPU host code vs GPU kernel debugging)

- Set strategic breakpoints (where you suspect the problem lies)

- Execute and inspect (step through code, examine variables)

- Analyze patterns (memory access, thread behavior, race conditions)

This workflow works whether you’re debugging a simple array operation from Puzzle 01 or complex shared memory code from Puzzle 08.

Step 1: Preparing your code for debugging